- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358770 > LC87F74C8A (Sanyo Electric Co.,Ltd.) 8-bit 1-chip Microcontroller PDF資料下載

參數(shù)資料

| 型號: | LC87F74C8A |

| 廠商: | Sanyo Electric Co.,Ltd. |

| 英文描述: | 8-bit 1-chip Microcontroller |

| 中文描述: | 8位1片上微控制器 |

| 文件頁數(shù): | 9/21頁 |

| 文件大小: | 575K |

| 代理商: | LC87F74C8A |

LC87F74C8A

No.7825-9/21

Continued from preceding page.

Pin name

I/O

Function

Option

S24/PD0 to S31/PD7

I/O

Segment output for LCD

Can be used as general purpose input/output port (PD)

No

S32/PE0 to S39/PE7

I/O

Segment output for LCD

Can be used as general purpose input/output port (PE)

No

S40/PF0 to S47/PF7

I/O

Segment output for LCD

Can be used as general purpose input/output port (PF)

No

COM0/PL0 to

COM3/PL3

V1/PL4 to V3/PL6

I/O

Common output for LCD

Can be used as general purpose input port (PL)

No

I/O

LCD output bias power supply

Can be used as general purpose input port (PL)

Other functions :

AD input ports : AN12 to AN14

No

RES

I

Reset terminal

No

XT1

I

Input for 32.768kHz crystal oscillation

Other functions :

General purpose input port

AD input port : AN10

When not in use, connect to VDD1

Output for 32.768kHz crystal oscillation

Other functions :

General purpose input port

AD input port : AN11

When not in use, set to oscillation mode and leave open

No

XT2

I/O

No

CF1

I

Input terminal for ceramic oscillator

No

CF2

O

Output terminal for ceramic oscillator

No

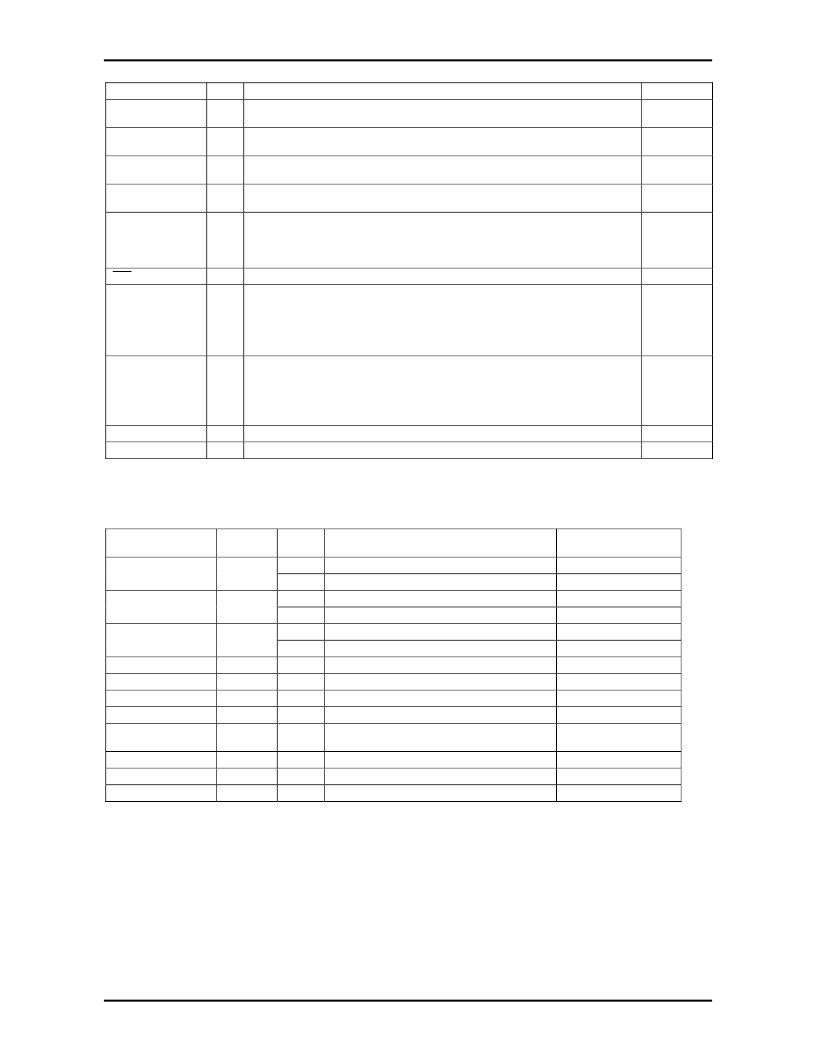

Port output Configuration

Port form and pull-up resistor options are shown in the following table.

Port status can be read even when port is set to output mode.

Option

applies to :

Terminal

Option

Output format

Pull-up resistor

1

CMOS

Programmable (Note 1)

P00 to P07

each bit

2

Nch-open drain

None

1

CMOS

Programmable

P10 to P17

each bit

2

Nch-open drain

Programmable

1

CMOS

Programmable

P30 to P35

each bit

2

Nch-open drain

None

P70

–

None

Nch-open drain

Programmable

P71 to P73

–

None

CMOS

Programmable

P80 to P87

–

None

Nch-open drain

None

S0/PA0 to S47/PF7

–

None

CMOS

Programmable

COM0/PL0 to

COM3/PL3

–

None

Input only

None

V1/PL4 to V3/PL6

–

None

Input only

None

XT1

–

None

Input only

None

XT2

Note 1 : Attachment of Port 0 programmable pull-up resistors is controllable in nibble units (P00 to 03, P04 to 07).

* Note 1 : Connect as follows to reduce noise on VDD.

VSS1, VSS2 and VSS3 must be connected together and grounded.

* Note 2 : The power supply for the internal memory is VDD1 but it uses the VDD2 as the power supply for ports.

When the VDD2 is not backed up, the port level does not become "H" even if the port latch is in the "H" level.

Therefore, when the VDD2 is not backed up and the port latch is "H" level, the port level is unstable in the

HOLD mode, and the back up time becomes shorter because the through current runs from VDD to GND in the

input buffer.

If VDD2 is not backed up, output "L" by the program or pull the port to "L" by the external circuit in the

HOLD mode so that the port level becomes "L" level and unnecessary current consumption is prevented.

–

None

Output for 32.768kHz crystal oscillation

None

相關PDF資料 |

PDF描述 |

|---|---|

| LC8900KQ | Digital Audio Interface Receiver |

| LC8901 | Digital Audio Interface Receiver |

| LC8901Q | Digital Audio Interface Receiver |

| LC8902Q | Digital Audio Interface Receiver(數(shù)字音頻接口接收器) |

| LC8903 | Digital Audio Interface Receiver(數(shù)字音頻接口接收器) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| LC87F76C8A | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:FROM 128K byte, RAM 4K byte on-chip 8-bit 1-chip Microcontroller |

| LC87F76C8AUEH-3E | 制造商:ON Semiconductor 功能描述:8-BIT MICROCONTROLLER - Trays |

| LC87F76C8AU-QFP-E | 制造商:ON Semiconductor 功能描述:8-BIT MICROCONTROLLER - Trays 制造商:ON Semiconductor 功能描述:8-bit Microcontrollers - MCU 8-BIT MCU 制造商:ON Semiconductor 功能描述:FTRAY / 8-BIT MICROCONTROLLER |

| LC87F76C8AU-TQFP-E | 功能描述:8位微控制器 -MCU RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風格:SMD/SMT |

| LC87F7932B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Ultra-low power consumption flash microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復。