- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄358770 > LC87F74C8A (Sanyo Electric Co.,Ltd.) 8-bit 1-chip Microcontroller PDF資料下載

參數(shù)資料

| 型號(hào): | LC87F74C8A |

| 廠商: | Sanyo Electric Co.,Ltd. |

| 英文描述: | 8-bit 1-chip Microcontroller |

| 中文描述: | 8位1片上微控制器 |

| 文件頁(yè)數(shù): | 12/21頁(yè) |

| 文件大小: | 575K |

| 代理商: | LC87F74C8A |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)當(dāng)前第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)

LC87F74C8A

No.7825-12/21

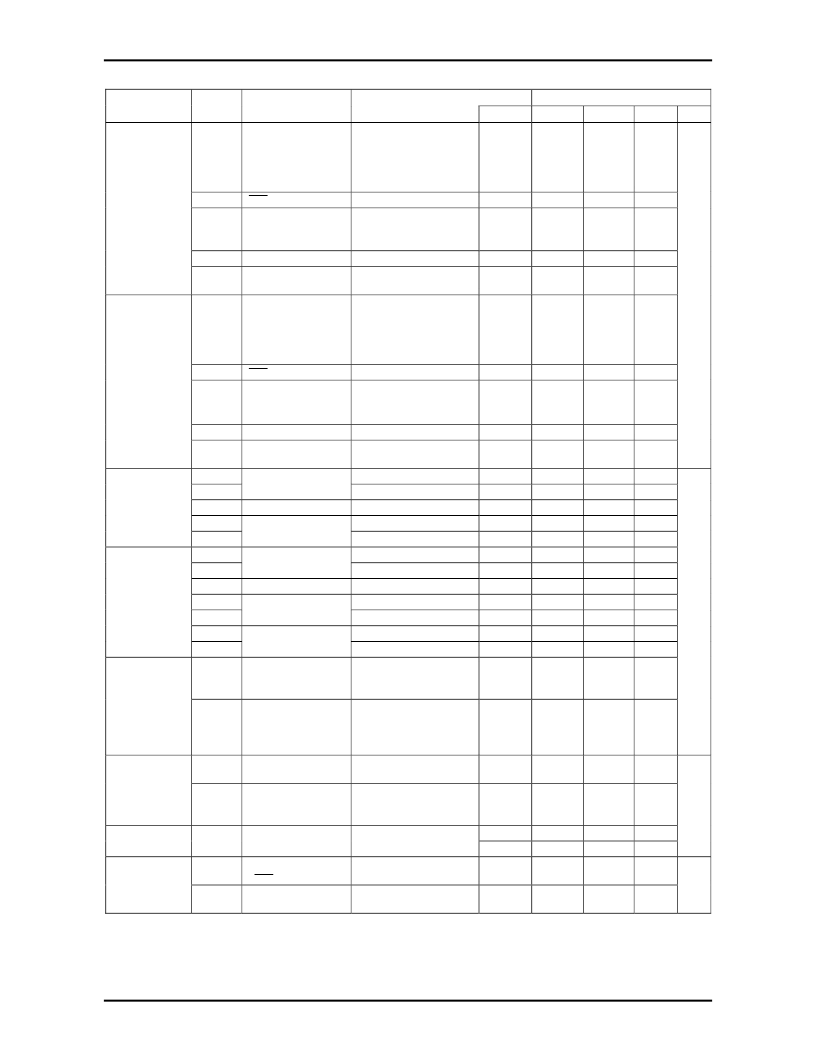

Electrical Characteristics

/ Ta = -20°C to +70°C, VSS1 = VSS2 = VSS3 = 0V

Limits

Parameter

Symbol

Pins

Conditions

VDD [V]

min

typ

max

unit

IIH(1)

Port 0, 1, 3, 7, 8

Port A, B, C, D, E, F, L

Output disabled

Pull-up resister OFF.

VIN = VDD

(Including OFF state leak

current of the output Tr.)

3.0 to 5.5

1

IIH(2)

IIH(3)

RES

VIN = VDD

When configured as an

input port

VIN = VDD

VIN = VDD

VIN = VBIS+0.5V

(VBIS : Bias voltage)

3.0 to 5.5

1

XT1, XT2

3.0 to 5.5

1

IIH(4)

IIH(5)

CF1

3.0 to 5.5

15

High level input

current

P87/AN7/MICIN

small signal input

3.0 to 5.5

4.2

8.5

15

IIL(1)

Port 0, 1, 3, 7, 8

Port A, B, C, D, E, F, L

Output disabled

Pull-up resister OFF.

VIN = VSS

(Including OFF state leak

current of the output Tr.)

3.0 to 5.5

-1

IIL(2)

IIL(3)

RES

VIN = VSS

When configured as an

input port

VIN = VSS

VIN = VSS

VIN = VBIS-0.5V

(VBIS : Bias voltage)

3.0 to 5.5

-1

XT1, XT2

3.0 to 5.5

-1

IIL(4)

IIL(5)

CF1

3.0 to 5.5

-15

Low level input

current

P87/AN7/MICIN

small signal input

3.0 to 5.5

-15

-8.5

-4.2

μ

A

VOH(1)

VOH(2)

VOH(3)

VOH(4)

VOH(5)

VOL(1)

VOL(2)

VOL(3)

VOL(4)

VOL(5)

VOL(6)

VOL(7)

VODLS

IOH = -1.0mA

IOH = -0.1mA

IOH = -0.4mA

IOH = -1.0mA

IOH = -0.1mA

IOL = 10mA

IOL = 1.6mA

IOL = 30mA

IOL = 1mA

IOL = 0.5mA

IOL = 8mA

IOL = 1.4mA

IO = 0mA

VLCD, 2/3VLCD, 1/3VLCD

level output Refer to figure 8

4.5 to 5.5

VDD-1

VDD-0.5

VDD-1

VDD-1

VDD-0.5

Port 0, 1, 3, CMOS

output option

3.0 to 5.5

Port 7

3.0 to 5.5

4.5 to 5.5

High level output

voltage

Port A, B, C, D, E, F

3.0 to 5.5

4.5 to 5.5

1.5

Port 0, 1, 3

3.0 to 5.5

0.4

Port 30, 31

4.5 to 5.5

1.5

4.5 to 5.5

0.4

Port 7, 8

3.0 to 5.5

0.4

4.5 to 5.5

1.5

Low level output

voltage

Port A, B, C, D, E, F

3.0 to 5.5

0.4

S0 to S47

3.0 to 5.5

0

± 0.2

LCD output

voltage regulation

VODLC

COM0 to COM3

IO = 0mA

VLCD, 2/3VLCD, 1/2VLCD

1/3VLCD level output

Refer to figure 8

3.0 to 5.5

0

± 0.2

V

RLCD(1)

Resistance per one bias

resistor

Refer to figure 8

3.0 to 5.5

60

LCD bias resistor

RLCD(2)

Resistance per one

bias resistor

1/2R mode

Refer to figure 8

3.0 to 5.5

30

4.5 to 5.5

15

40

70

Resistance of

pull-up MOS Tr.

Rpu

Port 0, 1, 3, 7

Port A, B, C, D, E, F

VOH = 0.9VDD

3.0 to 5.5

25

70

150

k

VHIS(1)

Port 1, 7

RES

Port 87 small signal

input

3.0 to 5.5

0.1VDD

Hysterisis voltage

VHIS(2)

3.0 to 5.5

0.1VDD

V

Continued on next page.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LC8900KQ | Digital Audio Interface Receiver |

| LC8901 | Digital Audio Interface Receiver |

| LC8901Q | Digital Audio Interface Receiver |

| LC8902Q | Digital Audio Interface Receiver(數(shù)字音頻接口接收器) |

| LC8903 | Digital Audio Interface Receiver(數(shù)字音頻接口接收器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LC87F76C8A | 制造商:SANYO 制造商全稱(chēng):Sanyo Semicon Device 功能描述:FROM 128K byte, RAM 4K byte on-chip 8-bit 1-chip Microcontroller |

| LC87F76C8AUEH-3E | 制造商:ON Semiconductor 功能描述:8-BIT MICROCONTROLLER - Trays |

| LC87F76C8AU-QFP-E | 制造商:ON Semiconductor 功能描述:8-BIT MICROCONTROLLER - Trays 制造商:ON Semiconductor 功能描述:8-bit Microcontrollers - MCU 8-BIT MCU 制造商:ON Semiconductor 功能描述:FTRAY / 8-BIT MICROCONTROLLER |

| LC87F76C8AU-TQFP-E | 功能描述:8位微控制器 -MCU RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:50 MHz 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| LC87F7932B | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Ultra-low power consumption flash microcontroller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。