- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67755 > LC72137M (SANYO SEMICONDUCTOR CO LTD) PLL FREQUENCY SYNTHESIZER, 40 MHz, PDSO20 PDF資料下載

參數(shù)資料

| 型號(hào): | LC72137M |

| 廠商: | SANYO SEMICONDUCTOR CO LTD |

| 元件分類: | PLL合成/DDS/VCOs |

| 英文描述: | PLL FREQUENCY SYNTHESIZER, 40 MHz, PDSO20 |

| 封裝: | MFP20 |

| 文件頁(yè)數(shù): | 22/22頁(yè) |

| 文件大小: | 348K |

| 代理商: | LC72137M |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)當(dāng)前第22頁(yè)

No. 5743-9/22

LC72137, 72137M

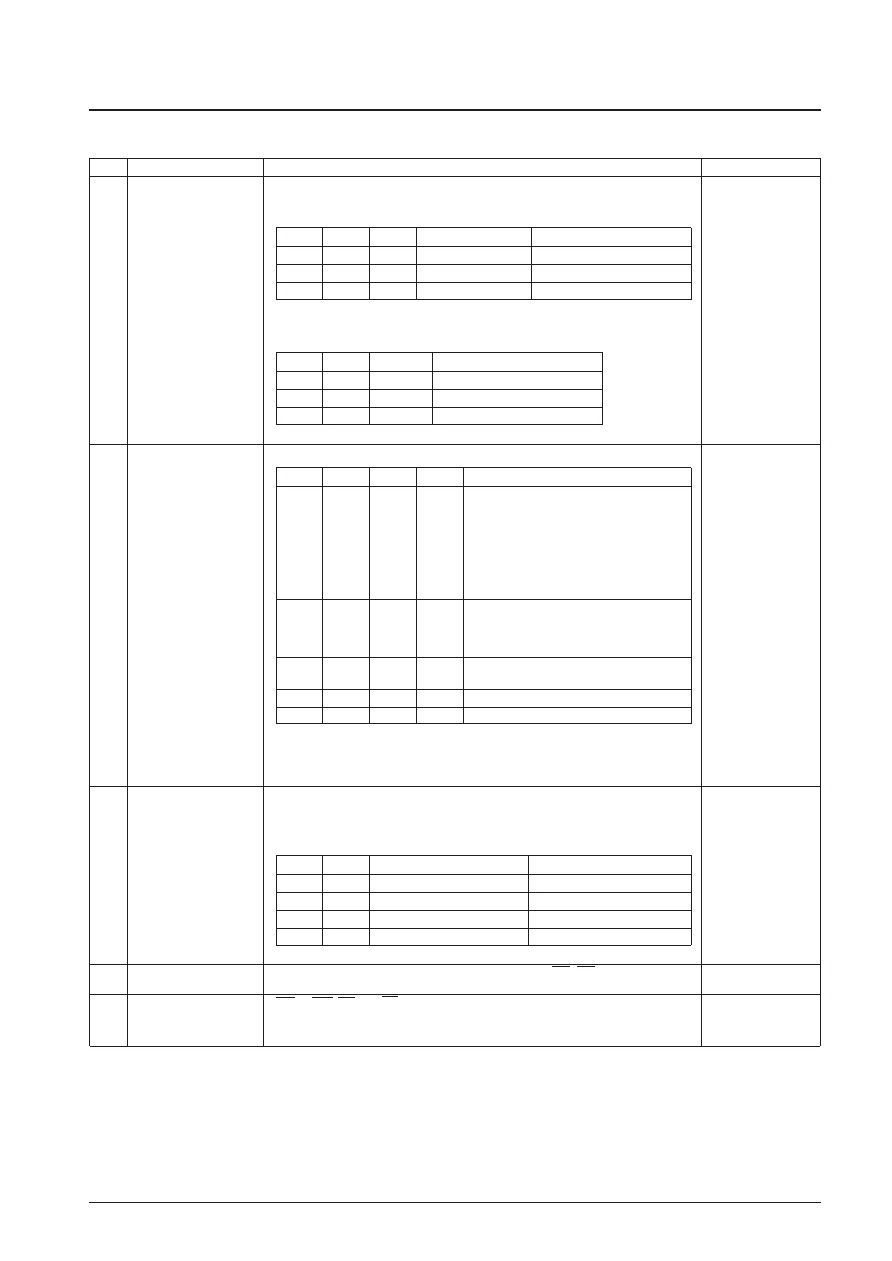

DI Control Data Descriptions

No.

Control block/data

Description

Related data

Programmable divider data Data that sets the programmable divider

P0 to P15

A binary value in which P15 is the MSB. The LSB changes depending on DVS and SNS.

(*: Don’t care.)

Note: P0 to P3 are ignored when P4 is the LSB.

DVS, SNS

Selects the signal input pin (AMIN or FMIN) for the programmable divider, switches the

frequency range. (*: Don’t care.)

Note: See the “Programmable Divider” item for details.

Reference divider data

Reference frequency (fref) selection data

R0 to R3

Note: PLL INHIBIT

The programmable divider and IF counter blocks are stopped, the FMIN, AMIN,

and IFIN pins go to the pulled-down state, and the charge pump output pin goes to

the high-impedance state.

IF counter control data

IF counter measurement start specification

CTE

CTE = 1: Counter start

CTE = 0: Counter reset

GT0, GT1

IF counter measurement time determination

Note: See the “IF Counter Structure” item for details.

I/O port specification data

Data that specifies input or output for the I/O dual-use pins (IO1, IO2)

IOC1, IOC2

Data: 0 = input mode, 1 = output mode

Output port data

BO1 to BO4, IO1, and IO2 output state data

BO1 to BO4, IO1, IO2

Data: 0 = open, 1 = low

“Data = 0: Open” is selected following a power-on reset.

(1)

(2)

(3)

(4)

(5)

IFS

IOC1

IOC2

DVS

SNS

LSB

Divisor setting (N)

Actual divisor

1

*

P0

272 to 65535

Twice the value of the setting

0

1

P0

272 to 65535

The value of the setting

0

P4

4 to 4095

The value of the setting

DVS

SNS

Input pin

Input frequency range

1

*

FMIN

10 to 160 MHz

0

1

AMIN

2 to 40 MHz

0

AMIN

0.5 to 10 MHz

GT1

GT0

Measurement time (ms)

Wait time (ms)

0

4

3 to 4

0

1

8

3 to 4

1

0

16

3 to 4

1

32

3 to 4

R3

R2

R1

R0

Reference frequency (kHz)

00

0

25

00

0

1

25

00

1

0

25

00

1

25

0

1

0

12.5

0

1

0

1

6.25

0

1

0

3.125

0

1

3.125

10

0

5

10

0

1

5

10

1

0

5

10

1

11

0

3

11

0

1

15

1

0

PLL INHIBIT + Xtal OSC STOP

1

PLL INHIBIT

Continued on next page.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LC72137 | PLL FREQUENCY SYNTHESIZER, 40 MHz, PDIP22 |

| LC72137M | PLL FREQUENCY SYNTHESIZER, 40 MHz, PDSO20 |

| LC99403 | SPECIALTY ANALOG CIRCUIT, BGA180 |

| LGDS-300-0-K/S | 1-OUTPUT DC-DC REG PWR SUPPLY MODULE |

| LGDS-300-0-K/T | 1-OUTPUT DC-DC REG PWR SUPPLY MODULE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LC72137MA-AE | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| LC72140 | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:PLL Frequency Synthesizers |

| LC72140M | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:PLL Frequency Synthesizers |

| LC72144M | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:PLL Frequency Synthesizer |

| LC72146 | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:PLL Frequency Synthesizer for Electronic Tuning |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。