- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358742 > LAN91C95 LAN Node Controller PDF資料下載

參數(shù)資料

| 型號(hào): | LAN91C95 |

| 英文描述: | LAN Node Controller |

| 中文描述: | 網(wǎng)絡(luò)節(jié)點(diǎn)控制器 |

| 文件頁(yè)數(shù): | 45/55頁(yè) |

| 文件大小: | 482K |

| 代理商: | LAN91C95 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)當(dāng)前第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)

FEAST Fast Ethernet Controller

for PCMCIA and Generic 16-Bit Applications

SMSC DS – LAN91C110 REV. B

Page 45

Rev. 09/05/02

In this case, the transmit interrupt service routine can find the next packet number to be serviced by reading the TX

FIFO PACKET NUMBER at the FIFO PORTS register. This eliminates the need for the driver to keep a list of packet

numbers being transmitted. The numbers are queued by the LAN91C110 and provided back to the CPU as their

transmission completes.

2. One interrupt per sequence of packets: Enable TX EMPTY INT and TX INT, set AUTO RELEASE=1. TX EMPTY

INT is generated only after transmitting the last packet in the FIFO.

TX INT will be set on a fatal transmit error allowing the CPU to know that the transmit process has stopped and

therefore the FIFO will not be emptied.

This mode has the advantage of a smaller CPU overhead, and faster memory de-allocation. Note that when AUTO

RELEASE=1 the CPU is not provided with the packet numbers that completed successfully.

Note

: The pointer register is shared by any process accessing the LAN91C110 memory. In order to allow processes

to be interruptable, the interrupting process is responsible for reading the pointer value before modifying it, saving it,

and restoring it before returning from the interrupt.

Typically there would be three processes using the pointer:

1. Transmit loading (sometimes interrupt driven)

2. Receive unloading (interrupt driven)

3. Transmit Status reading (interrupt driven).

1) and 3) also share the usage of the Packet Number Register. Therefore saving and restoring the PNR is also

required from interrupt service routines.

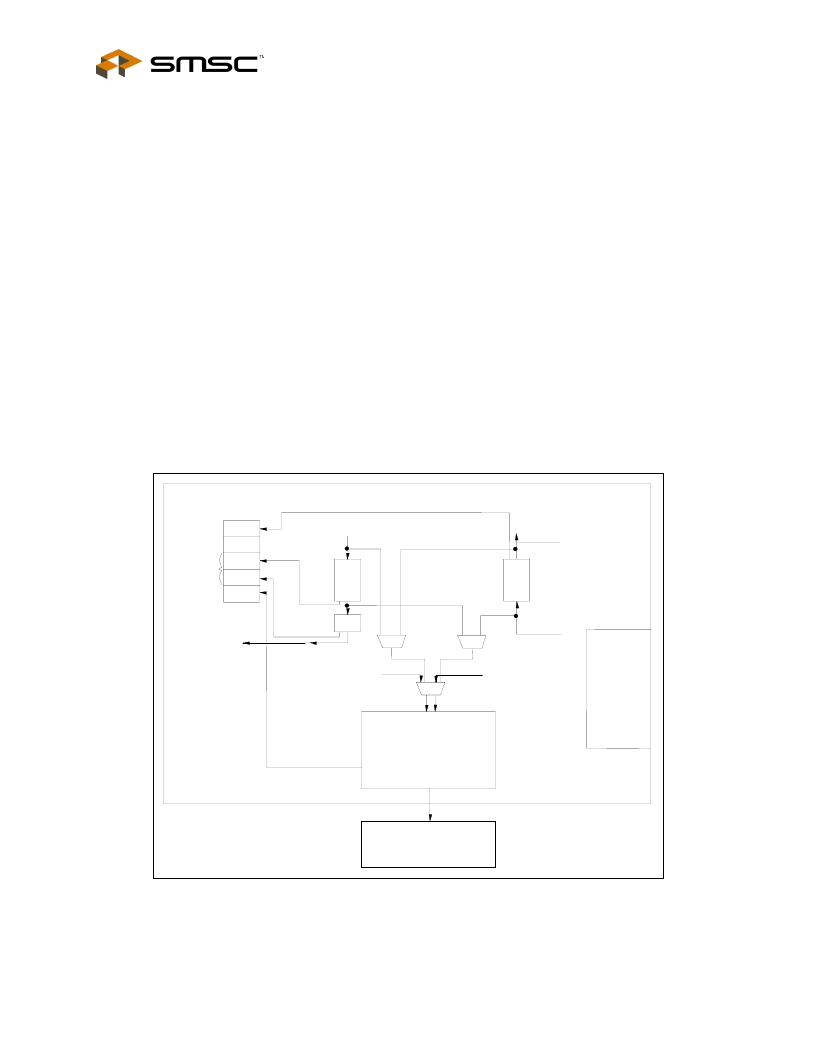

TX

FIFO

TX COFIFO

'NOT EMPTY'

RX

FIFO

CSMA/CD

LOGICAL

ADDRESS

PACKET #

MMU

PHYSICAL ADDRESS

RAM

CPU ADDRESS

CSMA ADDRESS

RX PACKET

NUMBER

RX FIFO

PACKET NUMBER

PACKET NUMBER

REGISTER

PACK # OUT

M.S. BIT ONLY

'EMPTY'

TX DONE

PACKET NUMBER

'NOT EMPTY'

INTERRUPT

STATUS REGISTER

RCV

INT

TX EMPTY

INT

TX

INT

ALLOC

INT

TWO

OPTIONS

FIGURE 12 - INTERRUPT GENERATION FOR TRANSMIT, RECEIVE, MMU

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LAN91C100FD(208TQFP) | LAN Node Controller |

| LAN91C100FD(208PQFP) | LAN Node Controller |

| LAN91C94 | ISA/PCMCIA SINGLE CHIP ETHERNET CONTROLLER WITH RAM |

| LAN91C110TQFP | FEAST FAST ETHERNET CONTROLLER FOR PCMCIA AND GENERIC 16-BIT APPLICATIONS |

| LAN91C96I | NON-PCI SINGLE-CHIP FULL DUPLES ETHERNET CONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LAN91C95TQFP | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:SMSC 功能描述: |

| LAN91C95TQFP WAF | 制造商:SMSC 功能描述: |

| LAN91C96 | 制造商:SMSC 功能描述: |

| LAN91C96(100QFP) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LAN Node Controller |

| LAN91C96(100TQFP) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LAN Node Controller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。