- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377598 > L64250JC15 (Innovasic Semiconductor) Histogram/Hough Transform Processor PDF資料下載

參數(shù)資料

| 型號(hào): | L64250JC15 |

| 廠商: | Innovasic Semiconductor |

| 英文描述: | Histogram/Hough Transform Processor |

| 中文描述: | 直方圖/ Hough變換處理器 |

| 文件頁數(shù): | 7/21頁 |

| 文件大小: | 100K |

| 代理商: | L64250JC15 |

IA64250

Histogram/Hough Transform Processor

Mode Definition:

The controller block decodes the instructions brought in to the IA64250 on the CI bus, with

the REGADR input determining which instructions are being read in. The Mode Memory

table shows the configuration of the CI bus encoded instruction depending on the state of

REGADR. A brief description of the instruction bits follows:

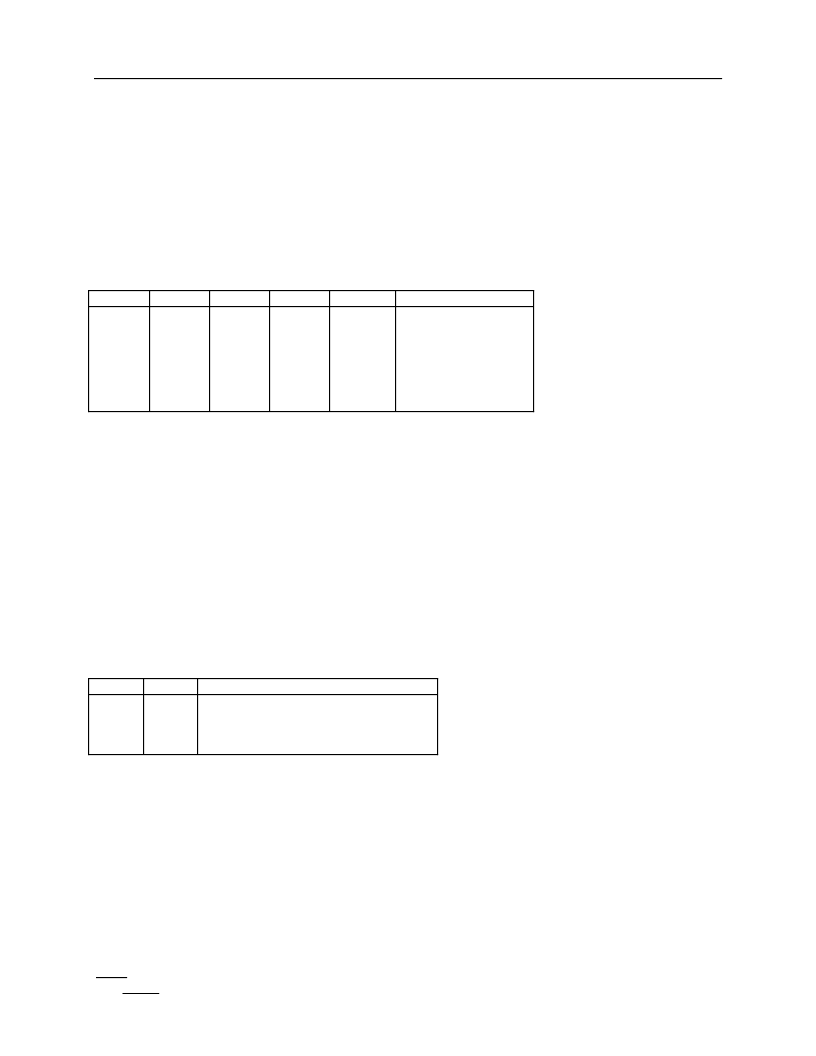

sel(3:0)

selects the nine bits of the ACC RAM to be transferred to the DO output or to the LUT

RAM.

sel0

sel1

sel2

sel3

Sel

window

0

1

0

1

0

…

1

1

1

1

15

select bits 15-23

lut(1:0)

defines one of the four 512 X 9 LUTs as active.

sh1

When low, the least significant nine bits of the 10 bit LUT and Y count sum will address the

ACC RAM. When high, the nine most significant bits of the sum will be used.

sat

When high, the nine bits selected from the 24 bit ACC RAM output will be forced to 511

(111111111) if the 24 bit ACC RAM output contains a 1 in the range of bits from the sel + 9

to 23. Otherwise the nine bits selected from the ACC RAM output will be unchanged.

test

Used for testing when low. Should be high for normal operation.

fn(1:0)

Determines the operation performed during the computational mode.

fn0

fn1

FUNCTION

0

0

1

1

1

pixel location

eq

When high, causes the output of the ACC RAM to be accumulated as it is read. This is

commonly used to compute the histogram equalization transfer function. When low, the

ACC RAM output is not modified.

Data Sheet

As of Production Ver. 01

Copyright

2000

innov

ASIC

The End of Obsolescence

ENG211001219-01

www.innovasic.com

Customer Support:

Page 7 of 21

1-888-824-4184

0

0

1

1

0

0

0

0

0

1

0

0

0

0

0

0

1

2

3

4

select bits 0-8

select bits 1-9

select bits 2-10

select bits 3-11

select bits 4-12

0

1

0

modified Hough transform computation

undefined

histogram computation

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| L64250JC20 | Histogram/Hough Transform Processor |

| L642DU12RE | 128 Megabit (8 M x 16-Bit) CMOS 3.0 Volt-only Uniform Sector Flash Memory with VersatileI/O⑩ Control |

| L642DU90RI | 128 Megabit (8 M x 16-Bit) CMOS 3.0 Volt-only Uniform Sector Flash Memory with VersatileI/O⑩ Control |

| L642DU12RI | 128 Megabit (8 M x 16-Bit) CMOS 3.0 Volt-only Uniform Sector Flash Memory with VersatileI/O⑩ Control |

| L64360 | Highly Integrated ATM Segmentation and Reassembly (SAR) Engine optimized for internetworking applications(用于優(yōu)化網(wǎng)絡(luò)的高度集成的異步傳輸模式-分段和重組處理芯片) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| L64250JC-15 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Image Processor |

| L64250JC20 | 制造商:INNOVASIC 制造商全稱:INNOVASIC 功能描述:Histogram/Hough Transform Processor |

| L64250JC-20 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Image Processor |

| L64260GC-30 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Digital Filter |

| L64260GC-40 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Digital Filter |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。