- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67710 > ICSSSTUB32871AHMLFT (INTEGRATED DEVICE TECHNOLOGY INC) 32871 SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 PDF資料下載

參數(shù)資料

| 型號: | ICSSSTUB32871AHMLFT |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 鎖存器 |

| 英文描述: | 32871 SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

| 封裝: | 5 X 11.50 MM, MO-205, TFBGA-96 |

| 文件頁數(shù): | 10/18頁 |

| 文件大小: | 199K |

| 代理商: | ICSSSTUB32871AHMLFT |

18

1186G—04/16/07

ICSSSTUB32871A

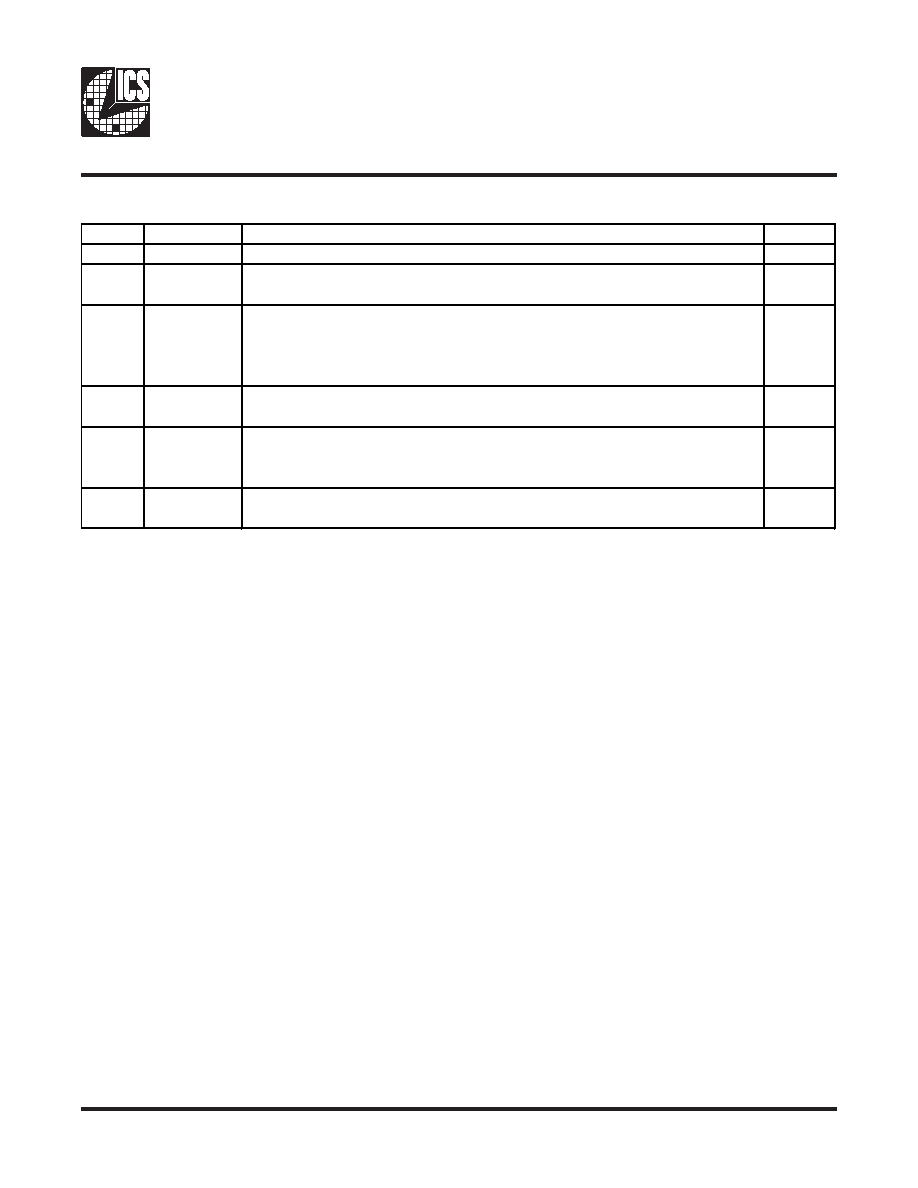

Revision History

Rev.

Issue Date Description

Page #

B

3/20/2006

Updated Ordering Information.

17

C

2/2/2007

Applications, 2nd bullet, changed ULP877 to ULPA877A, added

IDTCSPUA877A

1

D

3/1/2007

Page 1, Applications, 3rd bullet, removed 800; page 11, Electrical table,

changed Idd Operating Max from 80 to 150, changed

RESET Typ from 2.5

to 4.5; page 12, Timing table, changed ts (Data before...) from 0.5 to 0.6,

changed th (

DCS, DODT...) from 0.5 t

1, 11, 12

E

3/6/2007

Timing table, th hold time, changed Q to Dn; Switching Cha. Table, fixed

typos.

12

F

3/13/2007

Page 1, Recc. List, changed 3rd bullet to "Provides complete DDR DIMM

solution with ICS98ULPA877A, ICS97ULP877, or IDTCSPUA877A"; page

11, fixed typos.

1, 11

G

4/16/2007

Electrical Cha. Table, changed Ci: Data Inputs max from 3.5 to 5, and

CLK Max from 3 to 3.8.

11

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ICSSSTUF32864AYH-T | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

| ICSSSTUF32864AYHLF-T | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

| ICSSSTUF32864AYHLF-T | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

| ICSSSTUF32864YHLFT | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

| ICSSSTUF32866EHT | SSTU SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PBGA96 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ICSSSTUB32871AZLFT | 制造商:ICS 制造商全稱:ICS 功能描述:27-Bit Registered Buffer for DDR2 |

| ICSSSTUB32871AZT | 制造商:ICS 制造商全稱:ICS 功能描述:27-Bit Registered Buffer for DDR2 |

| ICSSSTUB32872A | 制造商:ICS 制造商全稱:ICS 功能描述:28-Bit Registered Buffer for DDR2 |

| ICSSSTUBF32866A | 制造商:ICS 制造商全稱:ICS 功能描述:25-Bit Configurable Registered Buffer for DDR2 |

| ICSSSTUBF32866AZ(LF)T | 制造商:ICS 制造商全稱:ICS 功能描述:25-Bit Configurable Registered Buffer for DDR2 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。