- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67682 > IBM25PPC405GPR-3BA333CZ 32-BIT, 333 MHz, RISC PROCESSOR, PBGA456 PDF資料下載

參數(shù)資料

| 型號(hào): | IBM25PPC405GPR-3BA333CZ |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 333 MHz, RISC PROCESSOR, PBGA456 |

| 封裝: | 35 MM, PLASTIC, EBGA-456 |

| 文件頁(yè)數(shù): | 47/56頁(yè) |

| 文件大?。?/td> | 1095K |

| 代理商: | IBM25PPC405GPR-3BA333CZ |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)當(dāng)前第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)

Preliminary

PowerPC 405GPr Embedded Processor Data Sheet

51

Strapping

When the SysReset input is driven low by an external device (system reset), the state of certain I/O pins is

read to enable default initial conditions prior to PPC405GPr start-up. The actual capture instant is the nearest

SysClk edge before the deassertion of reset. These pins must be strapped using external pull-up (logical 1) or

pull-down (logical 0) resistors to select the desired default conditions. The recommended pull-up is 3k

to

+3.3V or 10 k

to +5V. The recommended pull-down is 1K to GND. These pins are use for strap functions

only during reset. They are used for other signals during normal operation. The following tables list the

strapping pins along with their functions and strapping options.

The PPC405GPr can be used as a drop-in replacement for the PPC405GP. When the PPC405GPr is used

for this purpose, it should be strapped to operate in the PPC405GPr Legacy Mode. This option is selected by

strapping ball D20 (GPIO24) low (0). If Legacy Mode is selected, the “PPC405GPr Legacy Mode Strapping

Pin Assignments” table should be used to determine the strapping options. To operate the chip as a

PPC405GPr, strap D20 (GPIO24) high (1) and use “PPC405GPr New Mode Strapping Pin Assignments” on

page 75 to determine the strapping options.

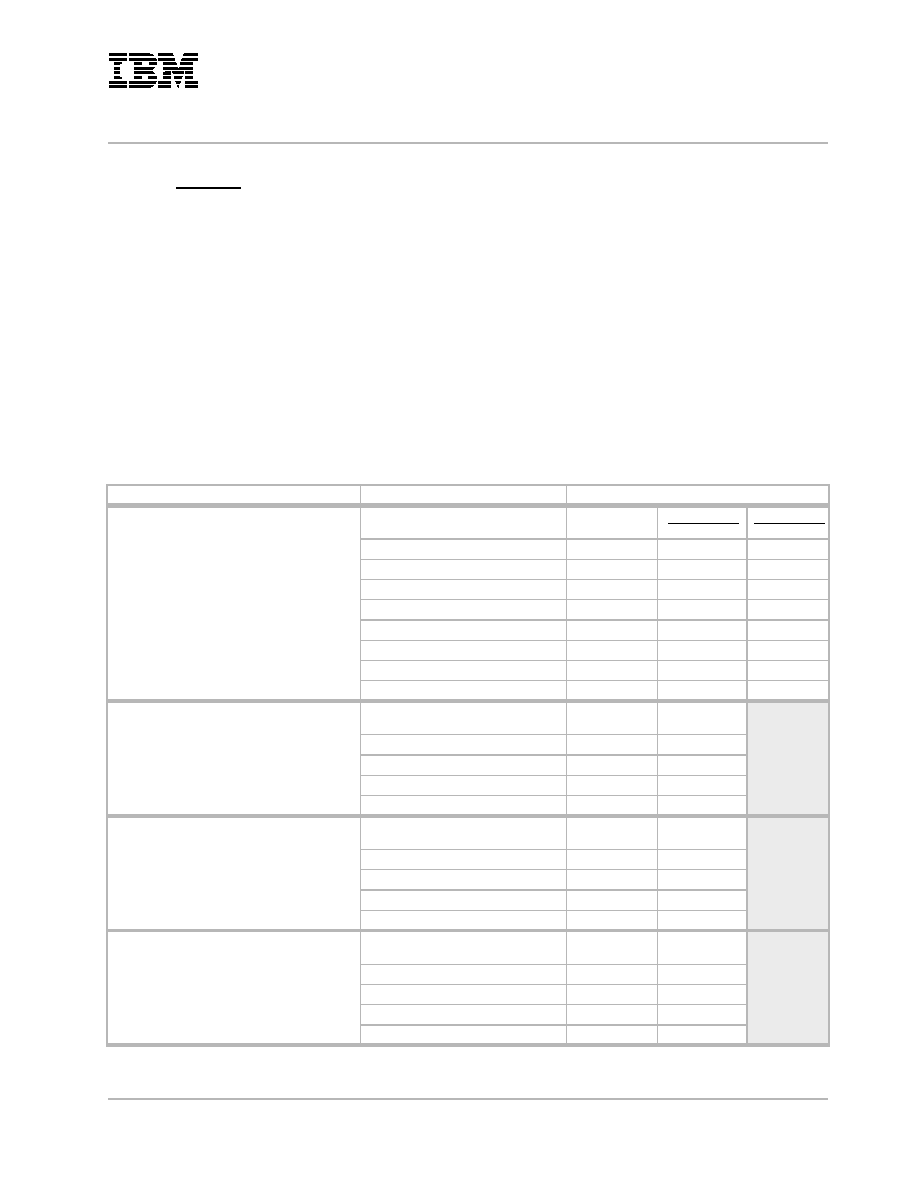

PPC405GPr Legacy Mode Strapping Pin Assignments (Part 1 of 2)

Function

Option

Ball Strapping

PLL Tuning 1

for 6

≤ M ≤ 7 use choice 3

for 7 < M

≤ 12 use choice 5

for 12 < M

≤ 32 use choice 6

AF3

(UART0_Tx)

AF2

(UART0_DTR)

AD16

(UART0_RTS)

Choice 1; TUNE[9:0] = 1010111100

0

Choice 2; TUNE[9:0] = 0100111000

0

1

Choice 3; TUNE[9:0] = 0100110110

0

1

0

Choice 4; TUNE[9:0] = 0100111100

0

1

Choice 5; TUNE[9:0] = 0100111000

1

0

Choice 6; TUNE[9:0] = 1000111100

1

0

1

Choice 7; TUNE[9:0] = 1000111110

1

0

Choice 8; TUNE[9:0] = 1011111110

1

PLL Forward Divider 2

D16

(DMAAck0)

B15

(DMAAck1)

Bypass mode

0

Divide by 3

0

1

Divide by 4

1

0

Divide by 6

1

PLL Feedback Divider 2

B14

(DMAAck2)

C12

(DMAAck3)

Divide by 1

0

Divide by 2

0

1

Divide by 3

1

0

Divide by 4

1

PLB Divider from CPU 2

P25

(EMCTxD3)

L24

(EMCTxD2)

Divide by 1

0

Divide by 2

0

1

Divide by 3

1

0

Divide by 4

1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IBM25PPC405GPR3DB400Z | 32-BIT, 400 MHz, RISC PROCESSOR, PBGA456 |

| IBM25PPC405GPR3BB400Z | 32-BIT, 400 MHz, RISC PROCESSOR, PBGA456 |

| IBM25PPC405GPR3DB266 | 32-BIT, 266 MHz, RISC PROCESSOR, PBGA456 |

| IBM25PPC603E-BX-133X | 32-BIT, 133 MHz, RISC PROCESSOR, CBGA255 |

| IBM25PPC603EV-FX-233X | 32-BIT, 233 MHz, RISC PROCESSOR, CQFP240 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IBM25PPC405GPR3BB266 | 制造商:IBM 功能描述: |

| IBM25PPC405-GPR-3JB266Z | 制造商:IBM 功能描述: |

| IBM25PPC405GPR-3KB266C | 制造商:IBM 功能描述: |

| IBM25PPC440GX3CB667C | 制造商:IBM 功能描述: |

| IBM25PPC603E-BX-080-X | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。