- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370806 > HYS72D256520GR (INFINEON TECHNOLOGIES AG) 184 Pin Registered Double Data Rate SDRAM Modules PDF資料下載

參數(shù)資料

| 型號: | HYS72D256520GR |

| 廠商: | INFINEON TECHNOLOGIES AG |

| 英文描述: | 184 Pin Registered Double Data Rate SDRAM Modules |

| 中文描述: | 184針注冊雙倍數(shù)據(jù)速率SDRAM模塊 |

| 文件頁數(shù): | 16/25頁 |

| 文件大小: | 638K |

| 代理商: | HYS72D256520GR |

HYS72D256520GR-7-A

Registered Double Data Rate SDRAM Modules

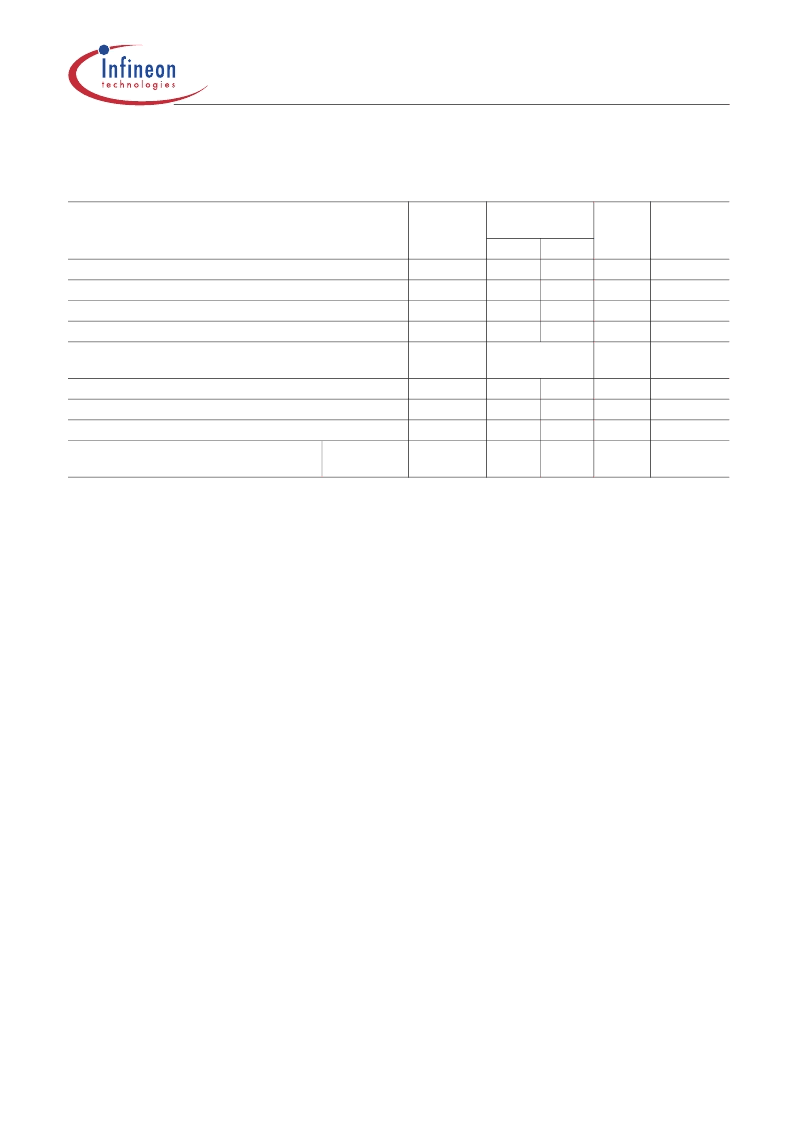

Electrical Characteristics

Data Sheet

16

Rev. 1.02, 2003-12

10282003-P6EY-RWQ2

Active to Read or Write delay

Precharge command period

Active bank A to Active bank B command

Write recovery time

Auto precharge write recovery

+ precharge time

Internal write to read command delay

Exit self-refresh to non-read command

Exit self-refresh to read command

Average Periodic Refresh Interval

t

RCD

t

RP

t

RRD

t

WR

t

DAL

20

20

15

15

(

t

WR

/

t

CK

) +

(

t

RP

/

t

CK

)

1

75

200

–

–

–

–

–

ns

ns

ns

ns

t

CK

1) to 4)

8)

1) to 4)

9)

1) to 4)

10)

1) to 4)

11)

1) to 4)9)

t

WTR

t

XSNR

t

XSRD

t

REFI

–

–

–

7.8

t

CK

ns

t

CK

μ

s

1) to 4)

1) to 4)

1) to 4)

512 Mbit

based

1) to 4)8)

1) Input slew rate >=1V/ns for DDR266.

2) The CK/CK input reference level (for timing reference to CK/CK) is the point at which CK and CK cross: the input reference

level for signals other than CK/CK, is VREF. CK/CK slew rate are >= 1.0 V/ns.

3) Inputs are not recognized as valid until VREF stabilizes.

4) The Output timing reference level, as measured at the timing reference point indicated in AC Characteristics (Note 3) is

VTT.

5) tHZ and tLZ transitions occur in the same access time windows as valid data transitions. These parameters are not referred

to a specific voltage level, but specify when the device is no longer driving (HZ), or begins driving (LZ).

6) The maximum limit for this parameter is not a device limit. The device operates with a greater value for this parameter, but

system performance (bus turnaround) degrades accordingly.

7) The specific requirement is that DQS be valid (HIGH, LOW, or some point on a valid transition) on or before this CK edge.

A valid transition is defined as monotonic and meeting the input slew rate specifications of the device. When no writes were

previously in progress on the bus, DQS will be transitioning from Hi-Z to logic LOW. If a previous write was in progress,

DQS could be HIGH, LOW, or transitioning from HIGH to LOW at this time, depending on tDQSS.

8) A maximum of eight Autorefresh commands can be posted to any given DDR SDRAM device.

9) For each of the terms, if not already an integer, round to the next highest integer. tCK is equal to the actual system clock

cycle time.

10) These parameters guarantee device timing, but they are not necessarily tested on each device

11) Fast slew rate >= 1.0 V/ns , slow slew rate >= 0.5 V/ns and < 1V/ns for command/address and CK & CK slew rate >1.0

V/ns, measured between VOH(ac) and VOL(ac)

Table 10

Electrical Characteristics & AC Timing for DDR components

(for reference only)

70

°

C

≤

T

A

≤

70

°

C;

V

DDQ

= 2.5 V

±

0.2 V;

V

DD

= 2.5 V

±

0.2 V

Parameter

Symbol

DDR266A

–

7

min.

Unit

Notes

max.

相關PDF資料 |

PDF描述 |

|---|---|

| HYS72D32000GR-7-A | Connectors, PCB header and jumpers Multipole |

| HYS72D128020GR-8-A | Cable Termination Tool; For Use With:MediaFlex and Interface Outlets, GigaFlex Modules; Connector Type:Modular RoHS Compliant: NA |

| HYS72D128020GR-8-B | Connector Wall Plate; Color:Almond; Leaded Process Compatible:Yes; No. of Ports:2 RoHS Compliant: Yes |

| HYS72D32000GR-8-A | Connectors, PCB header and jumpers Multipole RoHS Compliant: Yes |

| HYS72D64000GR-8-A | 2.5 V 184-pin Registered DDR-I SDRAM Modules |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| HYS72D256520GR-7 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x72 SDRAM Module |

| HYS72D256520GR-7-A | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:184 Pin Registered Double Data Rate SDRAM Modules |

| HYS72D256520GR-8 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DDR Synchronous DRAM |

| HYS72D256520GR-8-A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:?2GB (256Mx72) PC1600 2-bank available 3Q02? |

| HYS72D256920HBR-6-C | 制造商:QIMONDA 制造商全稱:QIMONDA 功能描述:184-Pin Registered Double-Data-Rate SDRAM Module |

發(fā)布緊急采購,3分鐘左右您將得到回復。