- 您現在的位置:買賣IC網 > PDF目錄370795 > HYE18P32161ACL70 (INFINEON TECHNOLOGIES AG) JT 23C 21#20 2#16 SKT PLUG PDF資料下載

參數資料

| 型號: | HYE18P32161ACL70 |

| 廠商: | INFINEON TECHNOLOGIES AG |

| 英文描述: | JT 23C 21#20 2#16 SKT PLUG |

| 中文描述: | 32M的異步/頁的CellularRAM |

| 文件頁數: | 17/33頁 |

| 文件大小: | 641K |

| 代理商: | HYE18P32161ACL70 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁

Data Sheet

17

V2.0, 2003-12-16

HYE18P32161AC(-/L)70/85

32M Asynch/Page CellularRAM

Functional Description

2.3.1

By applying PASR the user can dynamically customize the memory capacity to one’s actual needs in normal

operation mode and standby mode. With the activation of PASR there is no longer a power penalty paid for the

larger CellularRAM memory capacity in case only e.g. 8 MB are used by the host system.

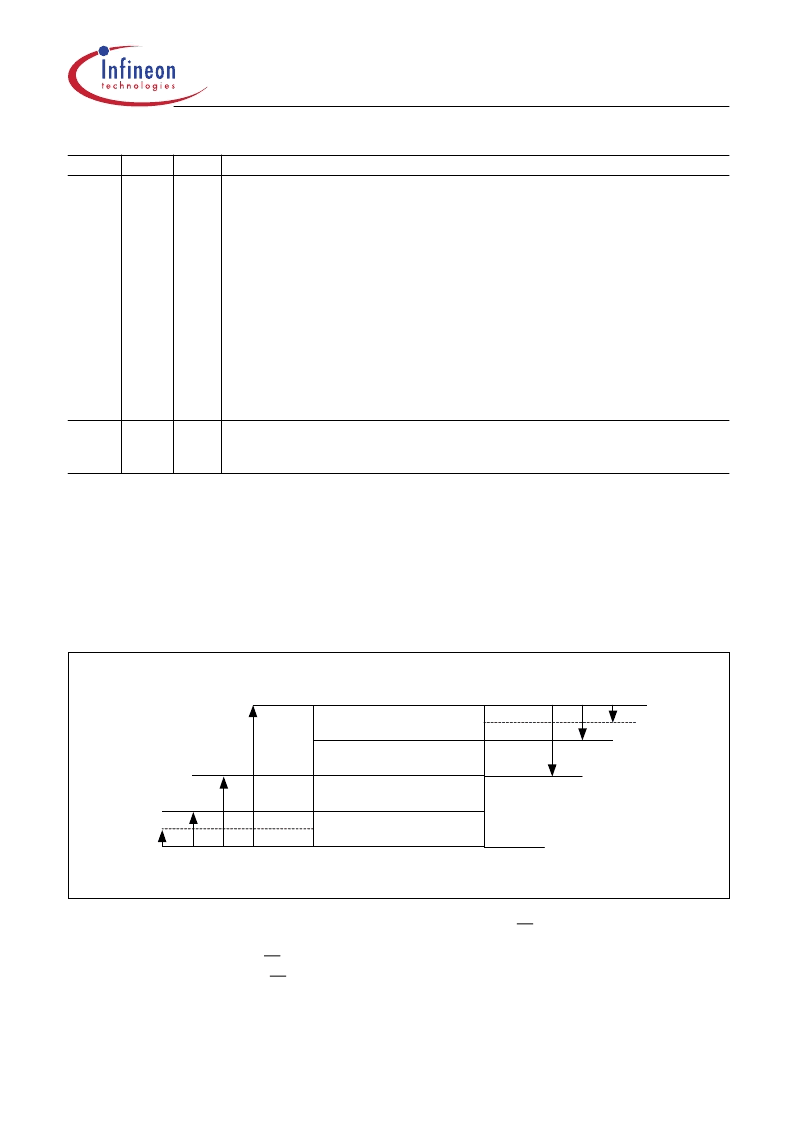

Bit2 down to bit0 specify the active memory array and its location (starting from bottom or top). The memory parts

not used are powered down immediately after the mode register has been programmed. Advice for the proper

register setting including the address ranges is given in

Figure 7

.

Partial Array Self Refresh (PASR)

Figure 7

PASR Programming Scheme

PASR is activated, i.e. the memory parts not used are powered down, after ZZ has been held low for more than

10μs. In PASR state no READ or WRITE commands are recognized. To resume WRITE or READ operations, the

device must exit PASR by taking ZZ to high level voltage again.

Pre-condition to enter PASR on ZZ low is that the Deep Power Down mode has been disabled before via

RCR.Bit4= 1.

Figure 8

shows an exemplary PASR configuration where it is assumed that the application uses max. 8 Mbit out

of 32 Mbit.

PASR

[2:0]

w

Partial Array Self Refresh

The 3-bit PASR field is used to specify the active memory array. The active memory

array will be kept periodically refreshed whereas the disabled parts will be excluded

from refresh and previously stored data will get lost. The normal operation still can be

executed in disabled array, but stored data is not guaranteed. This way the customer

can dynamically adapt the memory capacity in steps of 8 Mbit (4Mbit at the lowest) to

one’s need without paying a power penalty. Please refer to

Figure 7

.

000

entire memory array (default)

001

lower 1/2 of the memory array (16 Mb)

010

lower 1/4 of the memory array (8 Mb)

011

lower 1/8 of the memory array (4 Mb)

100

zero

101

upper 1/2 of the memory array (16 Mb)

110

upper 1/4 of the memory array (8 Mb)

111

upper 1/8 of the memory array (4 Mb)

Reserved

must be set to ‘0’

Res

20,

[18:8],

3

w

1) w: write-only access

Field

Bits

Type

1)

Description

8M

8M

8M

8M

000000h

07FFFFh

0FFFFFh

17FFFFh

1FFFFFh

000

32M

001

16M

010

8M

011

4M

1FFFFFh

180000h

100000h

080000h

000000h

100

101

110

111

PASR.Bit2,1,0

PASR.Bit2,1,0

4M

8M

16M

0M

相關PDF資料 |

PDF描述 |

|---|---|

| HYE18P32161ACL85 | Circular Connector; MIL SPEC:MIL-DTL-38999 Series II; Body Material:Metal; Series:JT; No. of Contacts:11; Connector Shell Size:18; Connecting Termination:Crimp; Circular Shell Style:Straight Plug; Body Style:Straight RoHS Compliant: No |

| HYE18P32161AC-70 | 32M Asynchronous/Page CellularRAM |

| HYE25L256160AC-75 | SMP(M)PIN CONT,PCB REAR MNT |

| HYE25L256160AF-7.5 | BJAWBMSpecialty DRAMs Mobile-RAM |

| HYE25L256160AC | 256-Mbit Mobile-RAM |

相關代理商/技術參數 |

參數描述 |

|---|---|

| HYE18P32161ACL85 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:32M Asynchronous/Page CellularRAM |

| HYE25L128160AC-7.5 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:BJAWBMSpecialty DRAMs Mobile-RAM |

| HYE25L128160AC-75 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:128-MBIT SYNCHRONOUS LOW-POWER DRAM IN CHIPSIZE PACKAGES |

| HYE25L128160AC-8 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:128-MBIT SYNCHRONOUS LOW-POWER DRAM IN CHIPSIZE PACKAGES |

發(fā)布緊急采購,3分鐘左右您將得到回復。