- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370783 > HYB25D128323CL3.6 (INFINEON TECHNOLOGIES AG) 128 Mbit DDR SGRAM PDF資料下載

參數(shù)資料

| 型號(hào): | HYB25D128323CL3.6 |

| 廠商: | INFINEON TECHNOLOGIES AG |

| 英文描述: | 128 Mbit DDR SGRAM |

| 中文描述: | 128兆的DDR SGRAM |

| 文件頁(yè)數(shù): | 36/53頁(yè) |

| 文件大小: | 1166K |

| 代理商: | HYB25D128323CL3.6 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)當(dāng)前第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)

HYB25D128323C[-3/-3.3/-3.6/-4.5/-5.0/L3.6/L4.5]

128 Mbit DDR SGRAM [4M x 32]

Register Set

Data Sheet

36

V1.7, 2003-07

Note:The Power Down Mode Entry command is illegal during Burst Read or Burst Write operations.

3.8

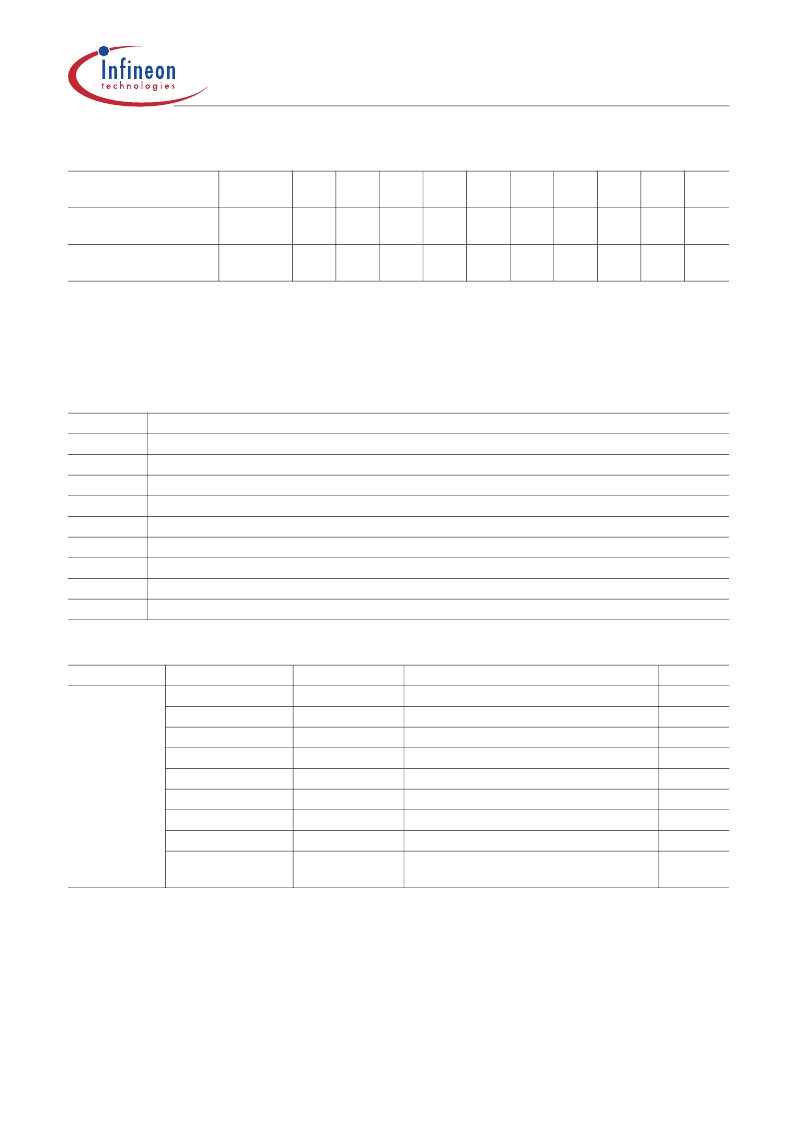

Function Truth Tables

Table 10

lists all abbreviations used in

Table 11

and

Table 12

.

Power Down Mode Entry

(Note)

Power Down Mode Exit

PWDNEN

H

H

L

L

L

H

H

L

H

L

X

H

X

valid

X

H

X

valid

X

H

X

valid

X

X

X

X

X

X

X

X

X

X

X

X

PWDNEX

Table 10

H

L

X

V

RA

BA

PA

NOP

CA

Ax

Abbreviations

High Level

Low Level

Don’t Care

Valid Data Input

Row Address

Bank Address

Precharge All

No Operation

Column Address

Address Line x

Table 11

Current State

IDLE

Function Truth Table I

Command

DESEL

NOP

BST

READ / READA

WRITE / WRITEA

ACT

PRE / PREAL

AREF / SREF

MRS / EMRS

Address

X

X

X

BA,CA,A8

BA,CA,A8

BA, RA

BA, A8

X

Op-Code

Action

NOP

NOP

NOP

ILLEGAL

ILLEGAL

Bank Active

NOP

AUTO-Refresh or Self-Refresh

Mode Register Set or Extended Mode

Register Set

Notes

3)

1)

3)

3)

2)

3)

3)

1)

4)

1)

1)

1)

4)

5)

4)

Table 9

Operation

Command Overview

(cont’d)

Code

CKE

n-1

CKE

n

CS#

RAS# CAS# WE#

BA0

BA1

A8

A0-7

A9-11

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYB25D128323C-3.3 | 128 Mbit DDR SGRAM |

| HYB25D128323C-3.6 | 128 Mbit DDR SGRAM |

| HYB25D128323C-4.5 | 128 Mbit DDR SGRAM |

| HYB25D128323C-5 | 128 Mbit DDR SGRAM |

| HYB25D128323C-L4.5 | 128 Mbit DDR SGRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYB25D128323CL4.5 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:128 Mbit DDR SGRAM |

| HYB25D128323C-L4.5 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:128 Mbit DDR SGRAM |

| HYB25D128323CL-4.5 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:128 Mbit DDR SGRAM |

| HYB25D128400AT | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:128 Mbit Double Data Rate SDRAM |

| HYB25D128400AT-6 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:128 Mbit Double Data Rate SDRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。