- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370783 > HYB25D128323CL3.6 (INFINEON TECHNOLOGIES AG) 128 Mbit DDR SGRAM PDF資料下載

參數(shù)資料

| 型號(hào): | HYB25D128323CL3.6 |

| 廠商: | INFINEON TECHNOLOGIES AG |

| 英文描述: | 128 Mbit DDR SGRAM |

| 中文描述: | 128兆的DDR SGRAM |

| 文件頁數(shù): | 30/53頁 |

| 文件大小: | 1166K |

| 代理商: | HYB25D128323CL3.6 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁當(dāng)前第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁

HYB25D128323C[-3/-3.3/-3.6/-4.5/-5.0/L3.6/L4.5]

128 Mbit DDR SGRAM [4M x 32]

Register Set

Data Sheet

30

V1.7, 2003-07

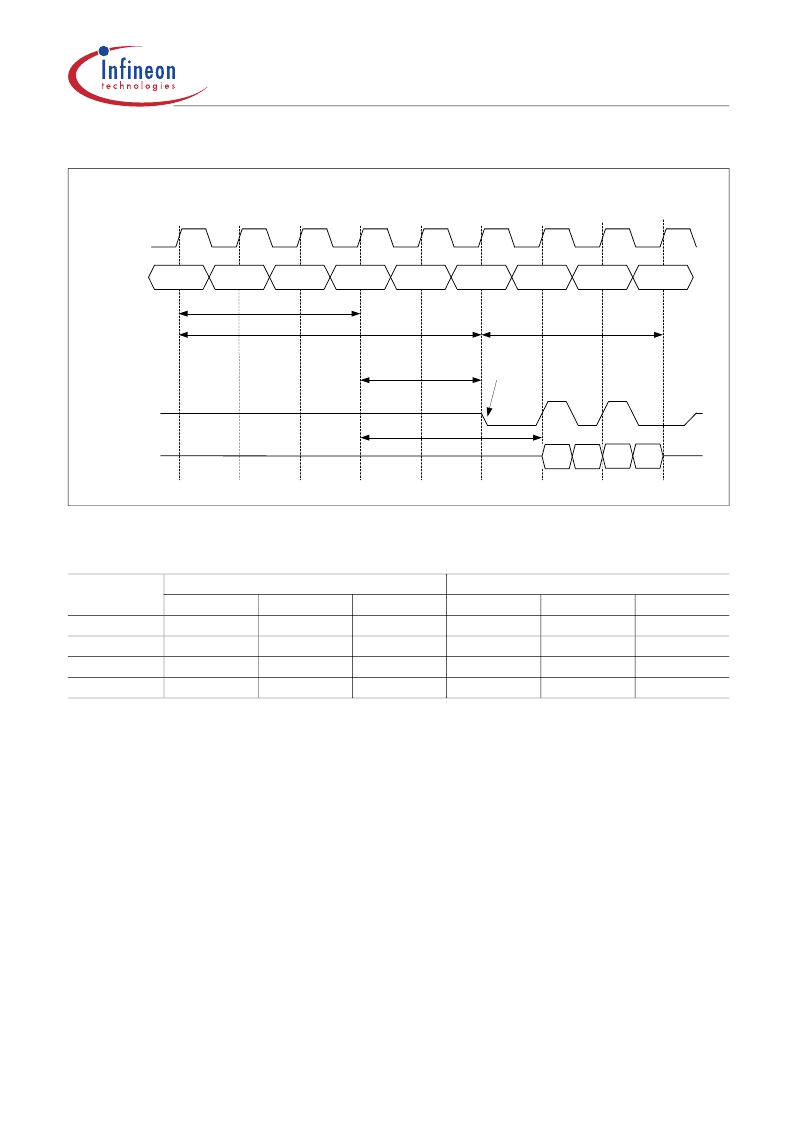

Figure 22

Read Concurrent Auto Precharge

Note:This table is for the case of Burst Length = 4, CAS Latency =3 and

t

WR

=2 clocks

When READ with Auto Precharge is asserted, new commands can be asserted at T4,T5 and T6 as shown in

Table 7

.

An Interrupt of a running READ burst with Auto Precharge i.e. at T4 and T5 to the same bank with another

READ+AP command is allowed, it will extend the begin of the internal Precharge operation to the last READ+AP

command.

Interrupts of a running READ burst with Auto Precharge i.e. at T4 are not allowed when doing concurrent

command to another active bank. ACTIVATE or PRECHARGE commands to another bank are always possible

while a READ with Auto Precharge operation is in progress.

3.5.16

If A8 is high when a Write command is issued, the Write with Auto-Precharge function is performed. The internal

precharge begins after the write recovery time

t

WR

and

t

RAS(min.)

are satisfied.

If a Write with Auto Precharge command is initiated, the DDR SGRAM automatically enters the precharge

operation at the first rising edge of CLK after the last valid edge of DQS (completion of the burst) plus the write

recovery time

t

WR

. Once the precharge operation has started, the bank cannot be reactivated and the new

command can not be asserted until the Precharge time (

t

RP

) has been satisfied. If

t

RAS(min.)

has not been satisfied

yet, an internal interlock will delay the precharge operation until it is satisfied.

Write with Autoprecharge (WRITEA)

Table 7

Asserted

Command

Concurrent Read Auto Precharge Support

For same Bank

T4

T5

NO

NO

YES

YES

NO

NO

PRECHARGE

YES

For different Bank

T4

NO

NO

YES

YES

T6

NO

NO

NO

NO

T5

YES

YES

YES

YES

T6

YES

YES

YES

YES

READ

READ+AP

ACTIVATE

YES

CLK

BANK A

ACTIVATE

Command

NOP

NOP

READ A

+ AP

NOP

NOP

Burst length = 4

DQSx

DQx

D-out

0

D-out

1

D-out

2

D-out

3

CAS latency = 3

CL = 3

Begin of

Auto Precharge

BL / 2

NOP

NOP

NOP

T0

T1

T2

T3

T4

T5

T6

T7

T8

t RCD(min)

t RAS(min)

t RP

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYB25D128323C-3.3 | 128 Mbit DDR SGRAM |

| HYB25D128323C-3.6 | 128 Mbit DDR SGRAM |

| HYB25D128323C-4.5 | 128 Mbit DDR SGRAM |

| HYB25D128323C-5 | 128 Mbit DDR SGRAM |

| HYB25D128323C-L4.5 | 128 Mbit DDR SGRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYB25D128323CL4.5 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:128 Mbit DDR SGRAM |

| HYB25D128323C-L4.5 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:128 Mbit DDR SGRAM |

| HYB25D128323CL-4.5 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:128 Mbit DDR SGRAM |

| HYB25D128400AT | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:128 Mbit Double Data Rate SDRAM |

| HYB25D128400AT-6 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:128 Mbit Double Data Rate SDRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。