- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371898 > HSP50016JC-52 (INTERSIL CORP) Digital Down Converter PDF資料下載

參數(shù)資料

| 型號: | HSP50016JC-52 |

| 廠商: | INTERSIL CORP |

| 元件分類: | 數(shù)字信號處理外設(shè) |

| 英文描述: | Digital Down Converter |

| 中文描述: | 16-BIT, DSP-MIXER, PQCC44 |

| 封裝: | PLASTIC, LCC-44 |

| 文件頁數(shù): | 1/31頁 |

| 文件大小: | 209K |

| 代理商: | HSP50016JC-52 |

當(dāng)前第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁

3-198

HSP50016

Digital Down Converter

The Digital Down Converter (DDC) is a single chip

synthesizer, quadrature mixer and lowpass filter. Its input

data is a sampled data stream of up to 16 bits in width and

up to a 75 MSPS data rate. The DDC performs down

conversion, narrowband low pass filtering and decimation to

produce a baseband signal.

The internal synthesizer can produce a variety of signal

formats. They are: CW, frequency hopped, linear FM up

chirp, and linear FM down chirp. The complex result of the

modulation process is lowpass filtered and decimated with

identical real filters in the in-phase (I) and quadrature (Q)

processing chains.

Lowpass filtering is accomplished via a High Decimation

Filter (HDF) followed by a fixed Finite Impulse Response

(FIR) filter. The combined response of the two stage filter

results in a -3dB to -102dB shape factor of better than 1.5.

The stopband attenuation is greater than 106dB. The

composite passband ripple is less than 0.04dB. The

synthesizer and mixer can be bypassed so that the chip

operates as a single narrow band low pass filter.

The chip receives forty bit serial commands as a control

input. This interface is compatible with the serial I/O port

available on most microprocessors.

The output data can be configured in fixed point or single

precision floating point. The fixed point formats are 16,

24, 32, or 38-bit, two’s complement, signed magnitude, or

offset binary.

The circuit provides an IEEE 1149.1 Test Access Port.

Features

75 MSPS Input Data Rate

16-Bit Data Input; Offset Binary or 2’s Complement

Format

Spurious Free Dynamic Range Through Modulator

>102dB

Frequency Selectivity: <0.006Hz

Identical Lowpass Filters for I and Q

Passband Ripple: <0.04dB

Stopband Attenuation: >104dB

Filter -3dB to -102dB Shape Factor: <1.5

Decimation Factors from 32 to 131,072

IEEE 1149.1 Test Access Port

HSP50016-EV Evaluation Board Available

Applications

Cellular Base Stations

Smart Antennas

Channelized Receivers

Spectrum Analysis

Related Products: HI5703, HI5746, HI5766 A/Ds

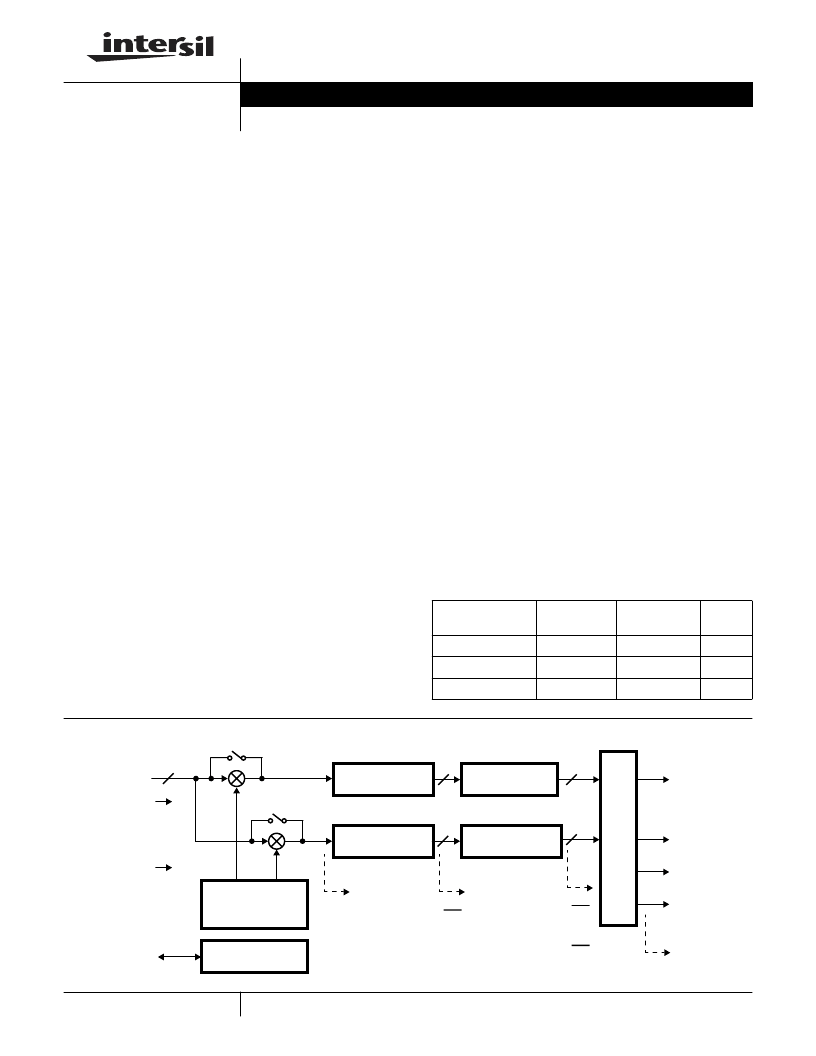

Block Diagram

Ordering Information

PART

NUMBER

TEMP.RANGE

(

o

C)

PACKAGE

PKG.

NO.

HSP50016JC-52

0 to 70

44 Ld PLCC

N44.65

HSP50016JC-75

0 to 70

44 Ld PLCC

N44.65

HSP50016GC-52

0 to 70

48 Ld CPGA

G48.A

COMPLEX

SINUSOID

GENERATOR

DATA

16

HIGH DECIMATION

FILTER

HIGH DECIMATION

FILTER

LOW PASS FIR

FILTER

LOW PASS FIR

FILTER

COS

SIN

I

Q

CONTROL

TEST ACCESS

PORT/CTRL

O

F

OUTPUT

I

Q

CLK

TEST ACCESS

PORT

CLK

CLK

R

CLK

4R

OR

CLK

2R

CLK

SER

IQSTRB

IQCLK

Data Sheet

February 1999

File Number

3288.6

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207

|

Copyright

Intersil Corporation 1999

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HSP50016JC-75 | Digital Down Converter |

| HSP50110JC-60 | Communications Tuner Circuit |

| HSP50306SC-25 | Digital QPSK Demodulator |

| HSP50306SC-2596 | Digital QPSK Demodulator |

| HSP50306SC-27 | Digital QPSK Demodulator |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HSP50016JC-5296 | 制造商:Rochester Electronics LLC 功能描述:TAPE AND REEL OF HSP50016JC-52 - Bulk |

| HSP50016JC-75 | 制造商:Rochester Electronics LLC 功能描述:DIGITAL DOWN CONVERTER 44 PLCC 75MHZ COMM - Bulk |

| HSP50016JI-52 | 制造商:Rochester Electronics LLC 功能描述:DIGITAL DOWN CONVERTER 44 PLCC, 52MHZ, COMM,INDS - Bulk |

| HSP50016JM-5296R3571 | 制造商:Intersil Corporation 功能描述:ROCKWELL HSP50016JC-5296 W/BRAND,-55/+125C OP TEMP,ELECTR - Tape and Reel |

| HSP50016JM-52R3571 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。