- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄370213 > FMS9875KGC140 Integrated Photo Flash Charger and IGBT Driver 16-QFN -35 to 85 PDF資料下載

參數(shù)資料

| 型號(hào): | FMS9875KGC140 |

| 英文描述: | Integrated Photo Flash Charger and IGBT Driver 16-QFN -35 to 85 |

| 文件頁(yè)數(shù): | 18/29頁(yè) |

| 文件大小: | 481K |

| 代理商: | FMS9875KGC140 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)當(dāng)前第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)

PRODUCT SPECIFICATION

FMS9875

18

REV. 1.2.15 1/14/02

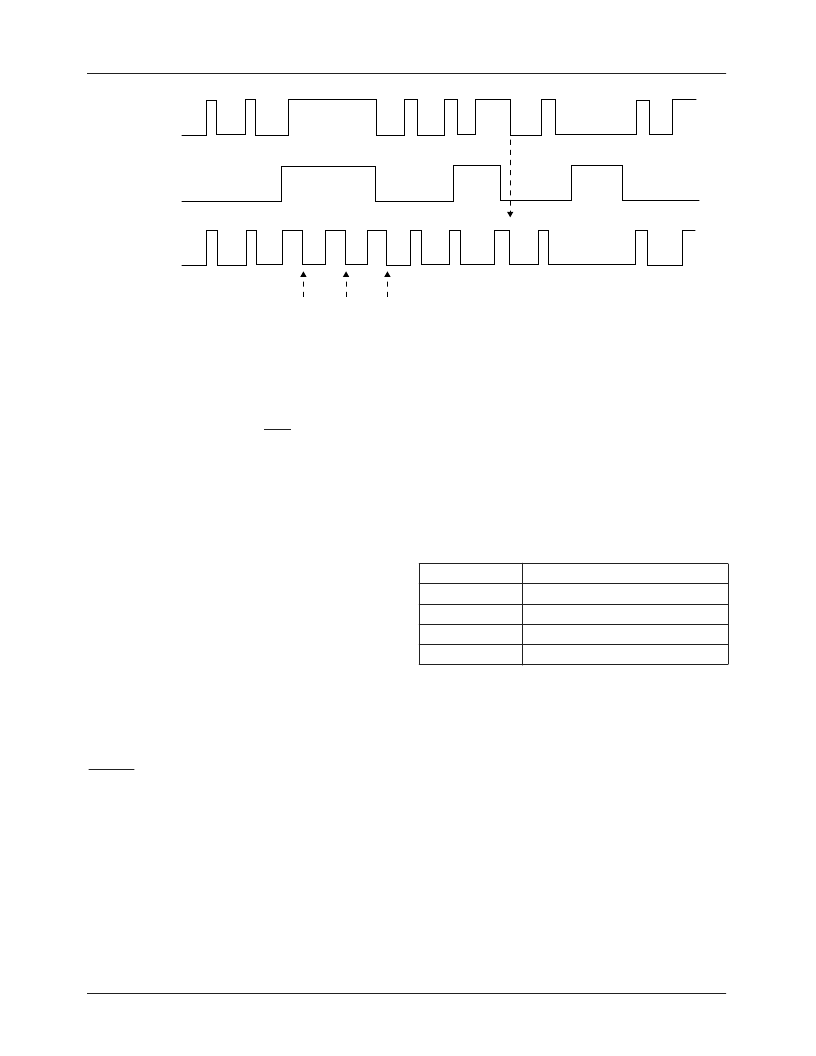

Figure 17.

50% Timeout

HSIN

COAST

HSOUT

Trailing edge terminates HSOUT

Timing Generator

Timing and Control logic generates:

1.

Internal sampling clock, SCK.

2.

Output data clocks, DCK and DCK.

3.

Output horizontal sync, HS

OUT

.

Internal clamp pulse, ICLAMP.

4.

With HSPOL set correctly, ICLAMP delay follows the trail-

ing edge of horizontal sync in (HSIN). Delay is set by the

CD register. Width of ICLAMP is set by the CW register.

Range of CD and CW values is 1–255 pixels.

Sync Stripper

Some video signals include embedded composite sync rather

than separate horizontal and vertical sync signals, typically

sync on green. Composite sync is extracted from Composite

Video at the ACS

IN

pin.

When the ACS

IN

signal falls below a 150mV ground refer-

enced threshold, sync is detected. Composite Sync Output,

DCS

OUT

reflects the ACS

IN

sync timing with non-inverted

CMOS digital levels.

Power Down

PWRDN = L minimizes FMS9875 power consumption.

Data outputs become high impedance. Clocks generation is

stopped. Register contents are retained. Sync stripping and

the internal voltage reference function.

Serial Interface

Register access is via a 2-wire I

2

C/SMBus compatible inter-

face. As a slave device, the 7-bit address is selected by the

A

1-0

pins (see Table 10). Serial port pins SDA and SCL com-

municate with the host SMBus/I

2

C controller which act as a

master.

Since the serial control port is design to interface with 3.3V

logic, the pins must be protected, if SDA and SCL signals

originate from 5V logic. Series connected 150

resistors are

recommended. (See Applications Section)

Table 10. Serial Interface Address Codes

Two signals comprise the bus: clock (SCL) and bi-directional

data (SDA). When receiving and transmitting data through

the serial interface, the FMS9875 acts as a slave, responding

only to commands by the I

2

C/SMBus master.

Data received or transmitted on the SDA line must be stable

for the duration of the positive-going SCL pulse. Data on

SDA may change only when SCL = L. An SDA transition

while SCL = H is interpreted as a start or stop signal.

A

1-0

00

01

10

11

7-Bit Address

4C

4D

4E

4F

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FMS9875KGC140X | |

| FMS988AKAC100 | Signal Conditioner |

| FMS988AKAC140 | Signal Conditioner |

| FMU1 | TRANSISTOR | SOT-143R |

| RU101K | TRANSISTOR | SOT-23 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FMS9875KGC140X | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述: |

| FMS9875KWC | 制造商:Fairchild Semiconductor Corporation 功能描述: |

| FMS9884A | 制造商:FAIRCHILD 制造商全稱(chēng):Fairchild Semiconductor 功能描述:3x8-Bit, 108/140/175 Ms/s Triple Video A/D Converter with Clamps |

| FMS9884AKAC100 | 功能描述:視頻模擬/數(shù)字化轉(zhuǎn)換器集成電路 MQFP RoHS:否 制造商:Texas Instruments 輸入信號(hào)類(lèi)型:Differential 轉(zhuǎn)換器數(shù)量:1 ADC 輸入端數(shù)量:4 轉(zhuǎn)換速率:3 Gbps 分辨率:8 bit 結(jié)構(gòu): 輸入電壓:3.3 V 接口類(lèi)型:SPI 信噪比: 電壓參考: 電源電壓-最大:3.45 V 電源電壓-最小:3.15 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:TCSP-48 封裝:Reel |

| FMS9884AKAC140 | 功能描述:視頻模擬/數(shù)字化轉(zhuǎn)換器集成電路 MQFP RoHS:否 制造商:Texas Instruments 輸入信號(hào)類(lèi)型:Differential 轉(zhuǎn)換器數(shù)量:1 ADC 輸入端數(shù)量:4 轉(zhuǎn)換速率:3 Gbps 分辨率:8 bit 結(jié)構(gòu): 輸入電壓:3.3 V 接口類(lèi)型:SPI 信噪比: 電壓參考: 電源電壓-最大:3.45 V 電源電壓-最小:3.15 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:TCSP-48 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。