- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67505 > FMS9874AKGC140 (FAIRCHILD SEMICONDUCTOR CORP) 3-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP100 PDF資料下載

參數(shù)資料

| 型號(hào): | FMS9874AKGC140 |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類: | ADC |

| 英文描述: | 3-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP100 |

| 封裝: | MQFP-100 |

| 文件頁數(shù): | 6/26頁 |

| 文件大小: | 454K |

| 代理商: | FMS9874AKGC140 |

第1頁第2頁第3頁第4頁第5頁當(dāng)前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁

PRODUCT SPECIFICATION

FMS9874A

14

REV. 1.2.10 1/14/02

Modes marked 2X are 2X-oversampled modes where the

number of samples per horizontal line is doubled. To select

this mode, the Phase-locked Loop Divide Ratio value must

changed from PLL1x to:

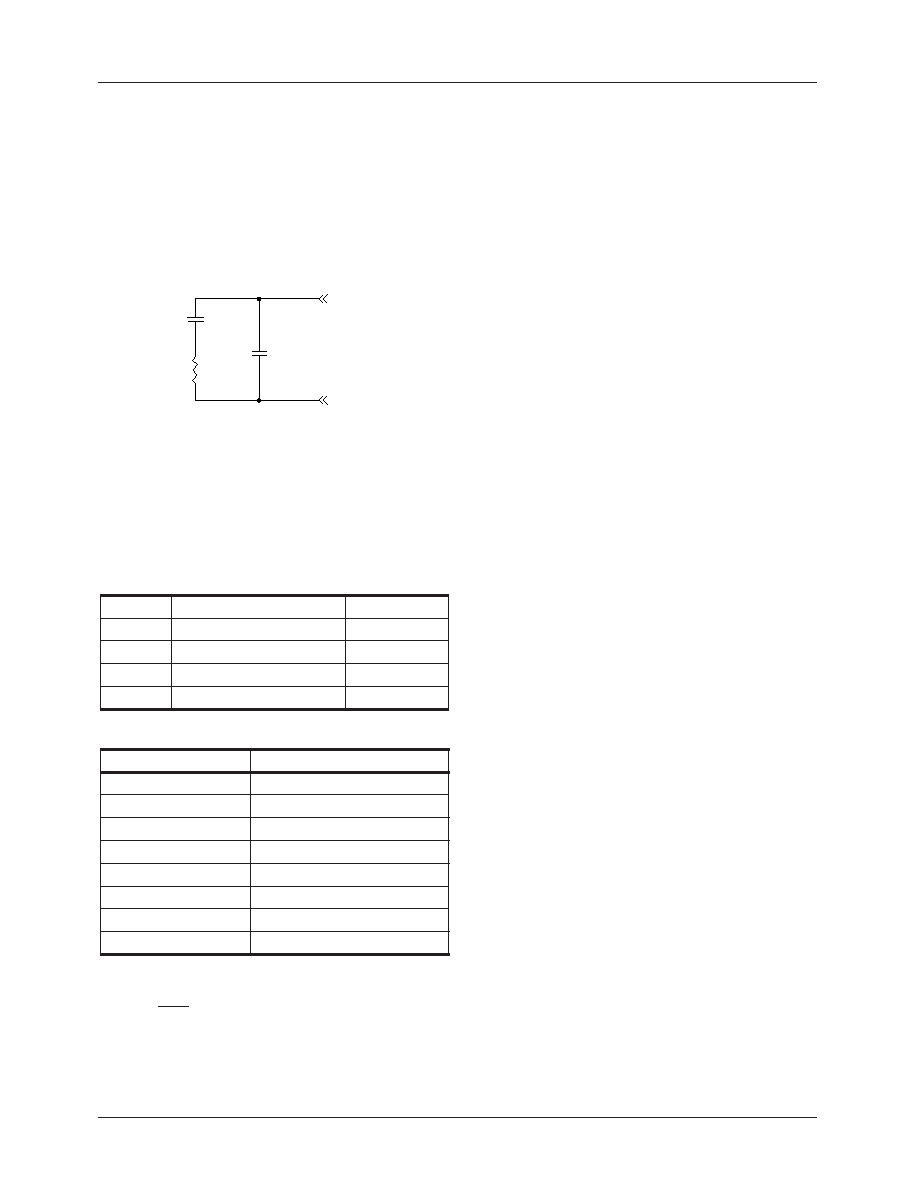

Values of IPUMP and FVCO are set through the PLL

Conguration Register (0x0C). Recommended external lter

components are shown in Figure 16. RF quality ±10%

ceramic capacitors with X7R dielectric are recommended.

Figure 16. Schematic, PLL Filter.

Loop performance is established by setting:

1.

VCO frequency range through FVCO1-0. (see Table 5)

2.

Charge Pump Current through IPUMP2-0. (see Table 6)

3.

External loop lter component values.

Setting PHASE4-0 selects the sampling phase of SCK rela-

tive to PXCK in 32 steps of 11.25°. Phase of the output data,

DCK and DCK is slaved to the SCK phase.

RMS Clock jitter is less than 2% of pixel period in all operat-

ing modes.

At frequencies below 80 MHz, the percentage jitter begins to

rise. Increased jitter at low frequencies can be counteracted

in either of two ways:

1.

Use 2X over-sampling. For example with NTSC-601,

the 1X sample rate should be 13.5 MHz. If the divide

ratio is increased from 858 (PLLN = 857) to 1716

(PLLN = 1715), the sampling rate is 27 MHz.

2.

Use 1X sampling by doubling the VCO frequency, then

dividing the PLL frequency by two. For example, with

NTSC-601, the divide ratio is doubled to 1716

(PLLN = 1715), then the sub-divide ratio is set to two

(PLLSUB1-0 = 01) to reduce the sampling rate from

27 MHz to 13.5 MHz with 858 pixels per line.

COAST

When COAST is active, PLL lock to HSIN is disabled, while

the VCO frequency is retained. VCO frequency remains

stable over several lines without updates from HSIN.

COAST can be connected directly to the vertical sync signal

or supplied by the graphics controller. If HSIN contains 1/2H

pulses, the COAST period must encompass all 1/2H pulses.

COAST polarity may be inverted using the COASTPOL

register bit. In the description below, the setting

COASTPOL = H is used.

Operation of COAST is depicted in Figure 17. HSOUT

polarity is always positive. When COAST = L, HSOUT

tracks HSIN (shown with postive polarity in Figure 1 ):

1.

HSOUT rising edge tracks HSIN delayed by a few pixels.

2.

HSOUT falling edge tracks the trailing edge of HSIN

with no delay.

When COAST = H, the PLL ywheels, disregarding the

incoming HSIN references, while the HSOUT waveform

depends upon the state of HSIN.

1.

If HSIN = H:

a.) HSOUT rising edge remains locked to the PLL.

b.) HSOUT trailing edge falls after 50% of the HSOUT

period has expired.

2.

HSIN transitions:

a.) HSOUT rising edge remains locked to the PLL.

b.) HSOUT falling edge is terminated by the trailing

edge of HSIN.

3.

If HSIN = L, then HSOUT = L

Table 5. VCO Frequency Bands

FVCO2-0 Frequency Range (MHz) KVCO (MHz/V)

00

10–40

35

01

10–70

60

10

20–120

80

11

20–150

95

Table 6. Charge Pump Currents

IPUMP2-0

Current (A)

000

50

001

100

010

150

011

250

100

350

101

500

110

750

111

1500

PLL

2x

2

PLL

1x

1

+

()

1

–

=

VDDP

LPF

C2

0.018

F

C1

0.18

F

R1

1.5K

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FMS9875KGC100 | 3-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP100 |

| FMS9875KGC100X | 3-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP100 |

| FMS9875KGC140 | 3-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP100 |

| FMS9875KGC140X | 3-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP100 |

| FN3410-10-44 | 500 V, 50 HZ, THREE PHASE EMI FILTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FMS9874KGC | 功能描述:視頻 IC RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| FMS9874KGC100 | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:Graphics Digitizer - 3x8-Bit, 108Ms/s Triple Video A/D Converter with Clamps |

| FMS9875 | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:Triple 8-Bit, 108/140 MHz A/D Converter with Clamps and PLL |

| FMS9875KAC100 | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:Triple 8-Bit, 108/140 MHz A/D Converter with Clamps and PLL |

| FMS9875KAC140 | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:Triple 8-Bit, 108/140 MHz A/D Converter with Clamps and PLL |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。