- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄19353 > EPF8452AQC160-4 (Altera)IC FLEX 8000A FPGA 4K 160-PQFP PDF資料下載

參數(shù)資料

| 型號(hào): | EPF8452AQC160-4 |

| 廠商: | Altera |

| 文件頁(yè)數(shù): | 14/62頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC FLEX 8000A FPGA 4K 160-PQFP |

| 產(chǎn)品培訓(xùn)模塊: | Three Reasons to Use FPGA's in Industrial Designs |

| 標(biāo)準(zhǔn)包裝: | 72 |

| 系列: | FLEX 8000 |

| LAB/CLB數(shù): | 42 |

| 邏輯元件/單元數(shù): | 336 |

| 輸入/輸出數(shù): | 120 |

| 門(mén)數(shù): | 4000 |

| 電源電壓: | 4.75 V ~ 5.25 V |

| 安裝類(lèi)型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 160-BQFP |

| 供應(yīng)商設(shè)備封裝: | 160-PQFP(28x28) |

| 產(chǎn)品目錄頁(yè)面: | 602 (CN2011-ZH PDF) |

| 其它名稱(chēng): | 544-2259 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)當(dāng)前第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)

Altera Corporation

21

FLEX 8000 Programmable Logic Device Family Data Sheet

FL

EX

800

0

3

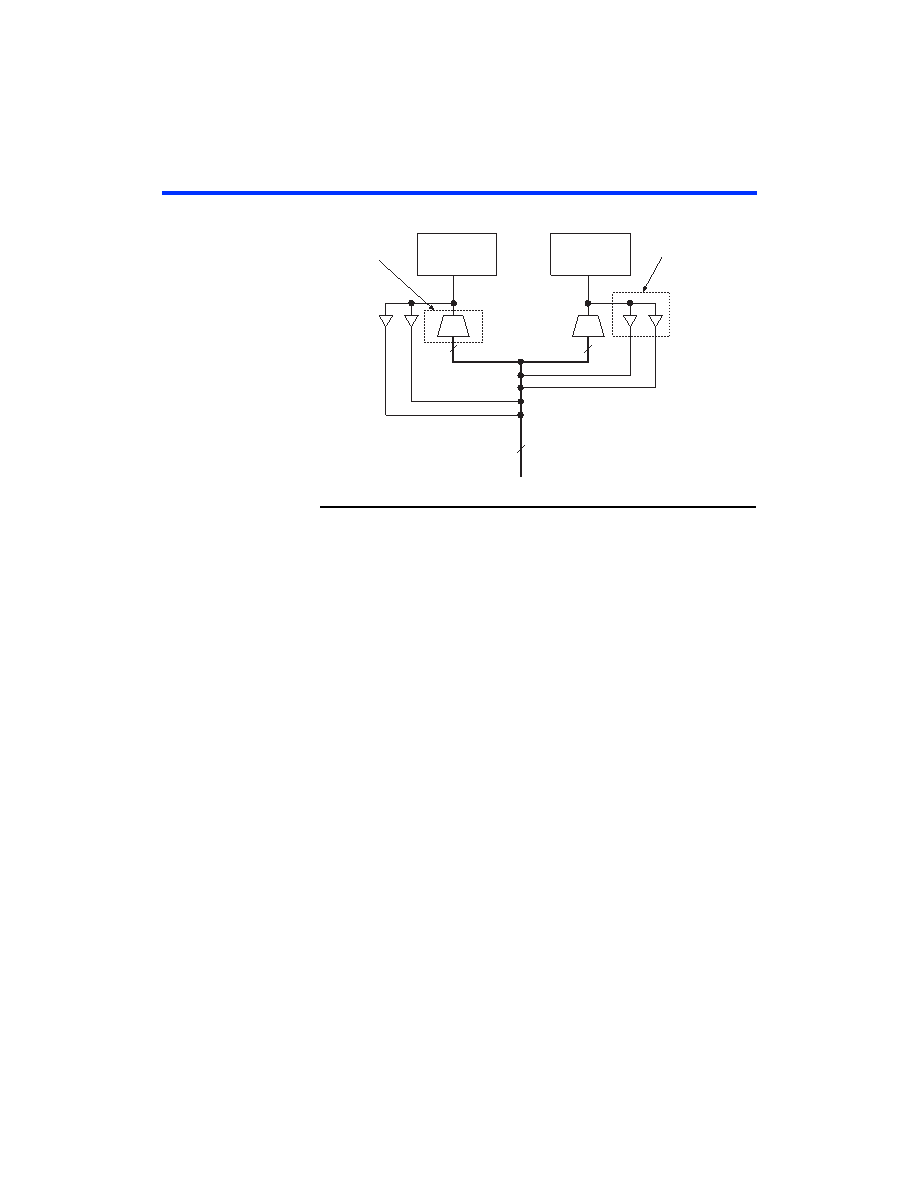

Figure 12. FLEX 8000 Column-to-IOE Connections

In addition to general-purpose I/O pins, FLEX 8000 devices have four

dedicated input pins. These dedicated inputs provide low-skew, device-

wide signal distribution, and are typically used for global clock, clear, and

preset control signals. The signals from the dedicated inputs are available

as control signals for all LABs and I/O elements in the device. The

dedicated inputs can also be used as general-purpose data inputs because

they can feed the local interconnect of each LAB in the device.

Signals enter the FLEX 8000 device either from the I/O pins that provide

general-purpose input capability or from the four dedicated inputs. The

IOEs are located at the ends of the row and column interconnect channels.

I/O pins can be used as input, output, or bidirectional pins. Each I/O pin

has a register that can be used either as an input register for external data

that requires fast setup times, or as an output register for data that

requires fast clock-to-output performance. The MAX+PLUS II Compiler

uses the programmable inversion option to invert signals automatically

from the row and column interconnect when appropriate.

The clock, clear, and output enable controls for the IOEs are provided by

a network of I/O control signals. These signals can be supplied by either

the dedicated input pins or by internal logic. The IOE control-signal paths

are designed to minimize the skew across the device. All control-signal

sources are buffered onto high-speed drivers that drive the signals around

the periphery of the device. This “peripheral bus” can be configured to

provide up to four output enable signals (10 in EPF81500A devices), and

up to two clock or clear signals. Figure 13 on page 22 shows how two

output enable signals are shared with one clock and one clear signal.

IOE

8

16

Column Interconnect

Each IOE is

driven by an

8-to-1

multiplexer.

Each IOE can drive

up to two column

signals.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 6-5174215-5 | CONN D-PLUG FEM SCKT 20POS VERT |

| VJ1206A820KBAAT4X | CAP CER 82PF 50V 10% NP0 1206 |

| EEC08DRYS-S734 | CONN EDGECARD 16POS DIP .100 SLD |

| VJ1206A820JBEAT4X | CAP CER 82PF 500V 5% NP0 1206 |

| LT3599EFE#PBF | IC LED DRVR WHITE BCKLGT 28TSSOP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EPF8452AQC160-4N | 制造商:Altera Corporation 功能描述:FPGA FLEX 8000 Family 4K Gates 336 Cells 125MHz CMOS Technology 5V 160-Pin PQFP |

| EPF8452AQC160-5 | 制造商:Altera Corporation 功能描述:Field-Programmable Gate Array, 336 Cell, 160 Pin, Plastic, QFP |

| EPF8452AQC160-6 | 制造商:Altera Corporation 功能描述: |

| EPF8452AQI160-3 | 制造商:Altera Corporation 功能描述:Field-Programmable Gate Array, 336 Cell, 160 Pin, Plastic, QFP |

| EPF8452ATC100-2 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。