- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378497 > CY7C1315BV18 (Cypress Semiconductor Corp.) 18-Mbit QDR-II SRAM 4-Word Burst Architecture(4字Burst結構,18-Mbit QDR-II SRAM) PDF資料下載

參數(shù)資料

| 型號: | CY7C1315BV18 |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | 18-Mbit QDR-II SRAM 4-Word Burst Architecture(4字Burst結構,18-Mbit QDR-II SRAM) |

| 中文描述: | 18兆位QDR - II型SRAM的4字突發(fā)架構(4字突發(fā)結構,18 - Mbit的QDR - II型的SRAM) |

| 文件頁數(shù): | 15/28頁 |

| 文件大小: | 459K |

| 代理商: | CY7C1315BV18 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

CY7C1311BV18

CY7C1911BV18

CY7C1313BV18

CY7C1315BV18

Document Number: 38-05620 Rev. *C

Page 15 of 28

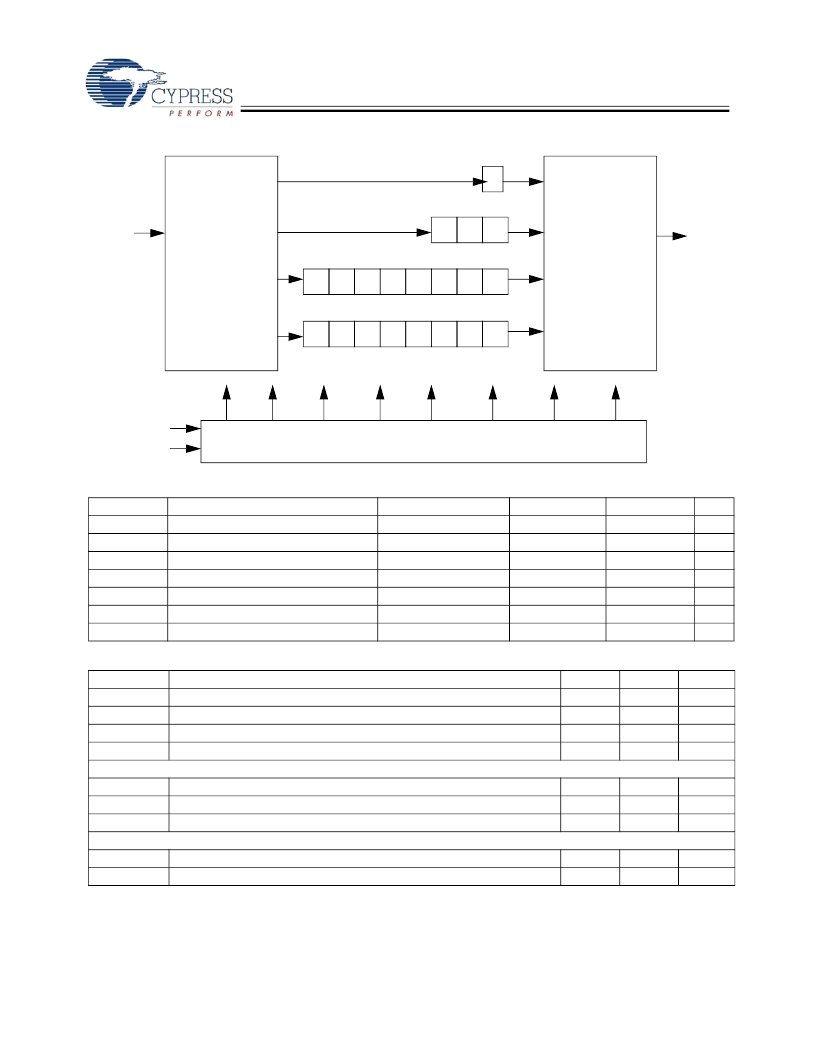

TAP Controller Block Diagram

TAP Electrical Characteristics

Over the Operating Range

[12, 15, 16]

Parameter

V

OH1

V

OH2

V

OL1

V

OL2

V

IH

V

IL

I

X

Description

Test Conditions

I

OH

=

2.0 mA

I

OH

=

100

μ

A

I

OL

= 2.0 mA

I

OL

= 100

μ

A

Min.

1.4

1.6

Max.

Unit

V

V

V

V

V

V

μ

A

Output HIGH Voltage

Output HIGH Voltage

Output LOW Voltage

Output LOW Voltage

Input HIGH Voltage

Input LOW Voltage

Input and Output Load Current

0.4

0.2

0.65V

DD

–0.3

–5

V

DD

+ 0.3

0.35V

DD

5

GND

≤

V

I

≤

V

DD

TAP AC Switching Characteristics

Over the Operating Range

[13, 14]

Parameter

t

TCYC

t

TF

t

TH

t

TL

Set-up Times

t

TMSS

t

TDIS

t

CS

Hold Times

t

TMSH

t

TDIH

Notes:

12.These characteristic pertain to the TAP inputs (TMS, TCK, TDI and TDO). Parallel load levels are specified in the Electrical Characteristics table.

13.t

and t

refer to the set-up and hold time requirements of latching data from the boundary scan register.

14.Test conditions are specified using the load in TAP AC test conditions. t

/t

= 1 ns.

15.Overshoot: V

(AC) < V

+ 0.85V (Pulse width less than t

CYC

/2), Undershoot: V

IL

(AC) >

1.5V (Pulse width less than t

CYC

/2).

16.All Voltage referenced to Ground.

Description

Min.

50

Max.

Unit

ns

MHz

ns

ns

TCK Clock Cycle Time

TCK Clock Frequency

TCK Clock HIGH

TCK Clock LOW

20

20

20

TMS Set-up to TCK Clock Rise

TDI Set-up to TCK Clock Rise

Capture Set-up to TCK Rise

5

5

5

ns

ns

ns

TMS Hold after TCK Clock Rise

TDI Hold after Clock Rise

5

5

ns

ns

0

0

1

2

.

.

29

30

31

Boundary Scan Register

Identification Register

0

1

2

.

.

.

.

106

0

1

2

Instruction Register

Bypass Register

Selection

Circuitry

Selection

Circuitry

TAP Controller

TDI

TDO

TCK

TMS

相關PDF資料 |

PDF描述 |

|---|---|

| CY7C1318AV18 | 18-Mbit DDR-II SRAM 2-Word Burst Architecture(18-Mb DDR-II SRAM(2-Word Burst結構)) |

| CY7C1316AV18 | 18-Mbit DDR-II SRAM 2-Word Burst Architecture |

| CY7C1316AV18-167BZC | 18-Mbit DDR-II SRAM 2-Word Burst Architecture |

| CY7C1318AV18-200BZC | 18-Mbit DDR-II SRAM 2-Word Burst Architecture |

| CY7C1318AV18-250BZC | 18-Mbit DDR-II SRAM 2-Word Burst Architecture |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C1315BV18-167BZC | 功能描述:靜態(tài)隨機存取存儲器 512Kx36 1.8V COM QDR II 靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1315BV18-167BZCT | 功能描述:靜態(tài)隨機存取存儲器 512Kx36 1.8V COM QDR II 靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1315BV18-200BZC | 功能描述:靜態(tài)隨機存取存儲器 512Kx36 1.8V COM QDR II 靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1315BV18-200BZI | 功能描述:靜態(tài)隨機存取存儲器 512Kx36 1.8V IND QDR II 靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1315BV18-200BZXC | 功能描述:靜態(tài)隨機存取存儲器 512Kx36 1.8V COM QDR II 靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復。