- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄256081 > B900J24FXX16IT 0-BIT, 59.88 MHz, OTHER DSP, PQFP44 PDF資料下載

參數(shù)資料

| 型號: | B900J24FXX16IT |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | 0-BIT, 59.88 MHz, OTHER DSP, PQFP44 |

| 文件頁數(shù): | 45/100頁 |

| 文件大?。?/td> | 1547K |

| 代理商: | B900J24FXX16IT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁當(dāng)前第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁

Lucent Technologies Inc.

49

Advance Data Sheet

B900

July 1999

Baseband Signal Processor

5 Software Architecture (continued)

5.2

Register Settings

The following tables, listed alphabetically, describe the programmable registers of the B900.

Note: Some tables in this section use the following abbreviations:

X = don’t care

W = write only

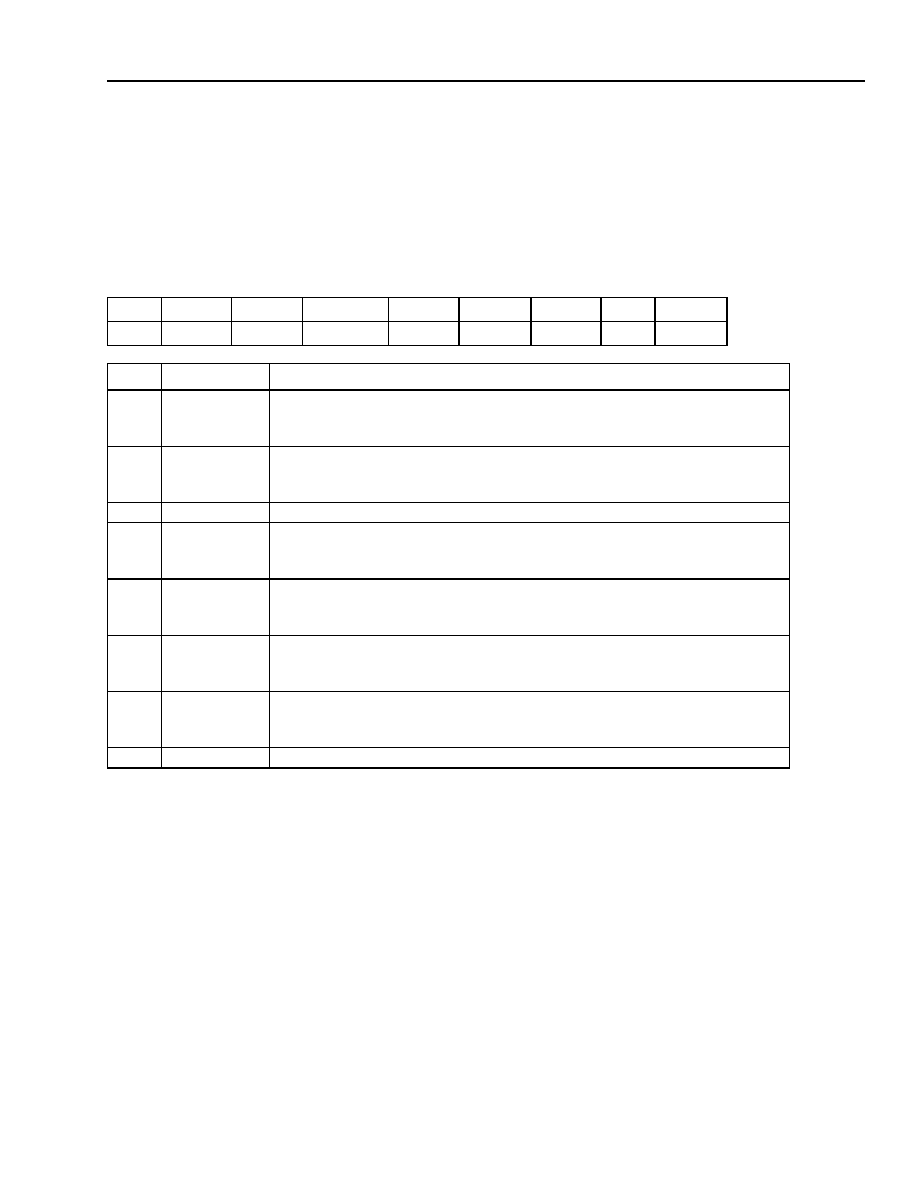

Table 36. alf (Standby and Memory Map) Register

Bit

15

14

13—8

7

6

5

4

3—0

Field

AWAIT

LOWPR

Res

NMNS1

MNS1

EVENP

ODDP

Res

Bit

Field

Description

15

AWAIT

Prepare DSP for standby:

0 = normal B900 operation.

1 = B900 enters standby, powerdown mode.

14

LOWPR

Memory map selection:

0 = select memory MAP1.

1 = select memory MAP3.

13—8

Res

Reserved—read as zero, write as zero.

7

NMNS1

Not minus one:

0 = BMU result is minus one in 2’s complement form.

1 = BMU result is not minus one in 2’s complement form.

6

MNS1

Minus one:

0 = BMU result is not minus one in 2’s complement form.

1 = BMU result is minus one in 2’s complement form.

5

EVENP

Even parity:

0 = BMU result has odd parity.

1 = BMU result has even parity.

4

ODDP

Odd parity:

0 = BMU result has even parity.

1 = BMU result has odd parity.

3—0

Res

Reserved—read as zero, write as zero.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| BU38703 | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP80 |

| BU-65170F6-10 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CDFP70 |

| BU-61580G6-12 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CDSO70 |

| BU-61585P2-11 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CPGA70 |

| BU-65170D5-30 | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| B-900-M-10 | 制造商:Thomas & Betts 功能描述: |

| B-900-M-10-EG | 制造商:Thomas & Betts 功能描述: |

| B-900-M-20 | 制造商:Thomas & Betts 功能描述: |

| B-900-M-20-EG | 制造商:Thomas & Betts 功能描述: |

| B901 | 制造商:EDAL 制造商全稱:EDAL 功能描述:Silicon Bridge Rectifier |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。