- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄382861 > AX88140A (Electronic Theatre Controls, Inc.) Fast Ethernet MAC Controller PDF資料下載

參數(shù)資料

| 型號(hào): | AX88140A |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Fast Ethernet MAC Controller |

| 中文描述: | 快速以太網(wǎng)MAC控制器 |

| 文件頁(yè)數(shù): | 13/46頁(yè) |

| 文件大小: | 467K |

| 代理商: | AX88140A |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)當(dāng)前第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)

AX88140A

PRELIMINARY

ASIX ELECTRONICS CORPORATION

13

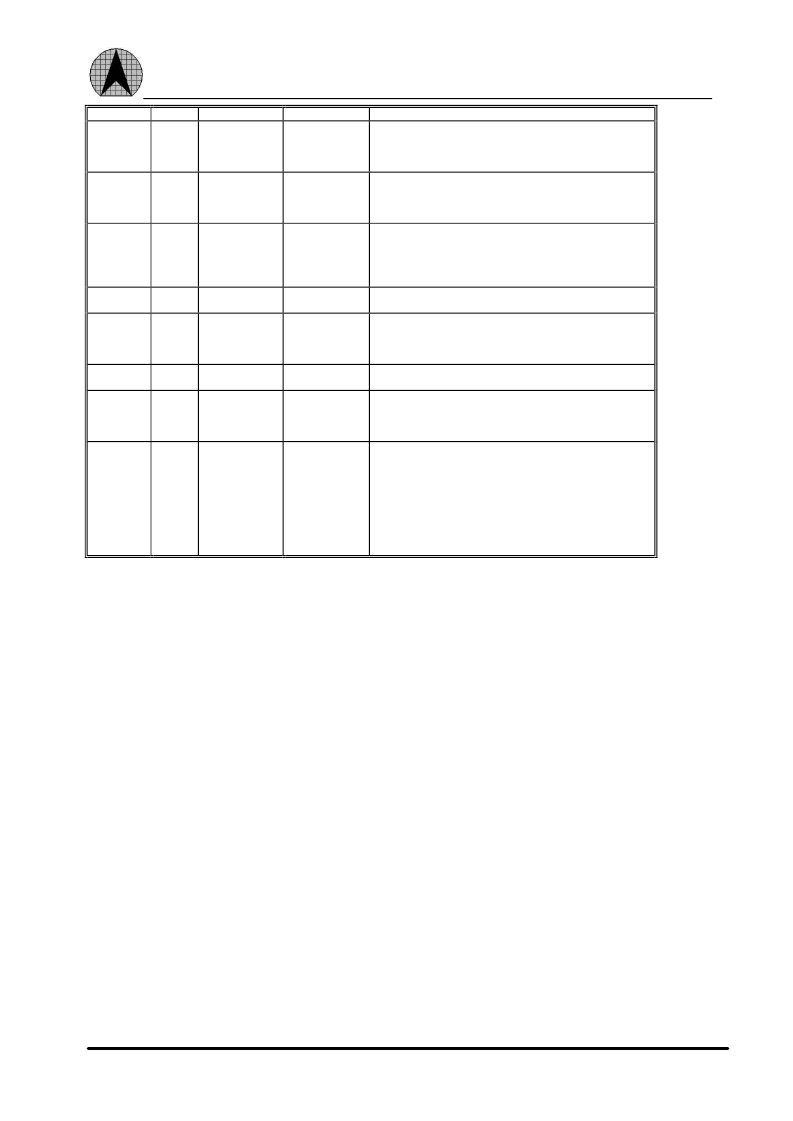

IRDY# to indicate that it is ready to accept data.

Parity is an even parity bit for the AD<31:0> AD and CBE#<3:0>.

During address and data phases, parity is calculated on all the

AD<31:0> AND CBE#<3:0>lines whether or not any of these

lines carry meaningful information.

The clock provides the timing for the AX88140A related PCI bus

transactions. All the bus signals are sampled on the rising edge of

PCI_CLK. The clock frequency range is between 21MHZ and

33MHZ.

Parity error asserts when a data parity error is detected. When the

AX88140A is the bus master it monitor PERR# to see if the target

report a data parity error., when the AX88140A is the bus target

and a parity error is detected, the AX88140A asserts PERR#. This

pin must be pulled up by an external resistor.

Bus request is asserted by the AX88140A to indicate to the bus

arbiter that it wants to use the bus.

Resets the AX88140A to its initial state. This signal must be

asserted for at least 10 active PCI clock cycles. When is the reset

state, all PCI output pins are put into tri-state and all PCI o/d

signals are floated.

System Error is used by AX88140A to report address parity Error.

This pin must be pulled up by an external resistor.

Stop indicator indicates that the current target is requesting the bus

master to stop the current transaction. The AX88140A responds to

the assertion of STOP# when it is the bus master, and stop the

current transaction.

Targetreadyindicatesthetargetabilitytocompletethecurrentdata

phase of the transaction.

A data phase is completed on any clock when both TRDY# and

IRDY# are asserted. Wait cycles are inserted until both IRDY#

and TRDY# are asserted together. When the AX88140A is the bus

master, target ready is asserted by the bus slave on the read

operation, indicating that valid data is present on the ad lines.

During a write cycle, it indicates that the target is prepared to

accept data.

PAR

I/O

53

47

PCI_CLK

I

7

5

PERR#

I/O

51

45

REQ#

O

10

8

RST#

I

4

2

SERR#

I/O

52

46

STOP#

I/O

49

43

TRDY#

I/O

47

41

Tab - 1 PCI interface group

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AX88140AP | Fast Ethernet MAC Controller |

| AX88140AQ | Fast Ethernet MAC Controller |

| AX88196 | 10/100BASE 3-in-1 Local CPU Bus Fast Ethernet Controller with Embedded SRAM |

| AX88196L | 10/100BASE 3-in-1 Local CPU Bus Fast Ethernet Controller with Embedded SRAM |

| AX88796 | 3-in-1 Local Bus Fast Ethernet Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AX88140AP | 制造商:ASIX 制造商全稱:ASIX 功能描述:Fast Ethernet MAC Controller |

| AX88140AQ | 制造商:ASIX 制造商全稱:ASIX 功能描述:Fast Ethernet MAC Controller |

| AX88141 | 制造商:ASIX 制造商全稱:ASIX 功能描述:100BASE-TX/FX PCI BUS FAST ETHERNET MAC CONTROLLER WITH POWER MANAGEMENT |

| AX88170L | 制造商:ASIX 制造商全稱:ASIX 功能描述:USB to Fast Ethernet/HomePNA Controller |

| AX88172 | 制造商:ASI 制造商全稱:ASI 功能描述:USB2.0 TO ETHERNET Device setup guide |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。