- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄362443 > AS4SD4M16A2-8 x16 SDRAM PDF資料下載

參數(shù)資料

| 型號: | AS4SD4M16A2-8 |

| 英文描述: | x16 SDRAM |

| 中文描述: | x16內(nèi)存 |

| 文件頁數(shù): | 22/51頁 |

| 文件大小: | 1071K |

| 代理商: | AS4SD4M16A2-8 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁

S DR A M

AS4SD16M16

Austin Semiconductor, Inc.

AS4SD16M16

Rev. 1.5 6/03

Austin Semiconductor, Inc. reserves the right to change products or specifications without notice.

22

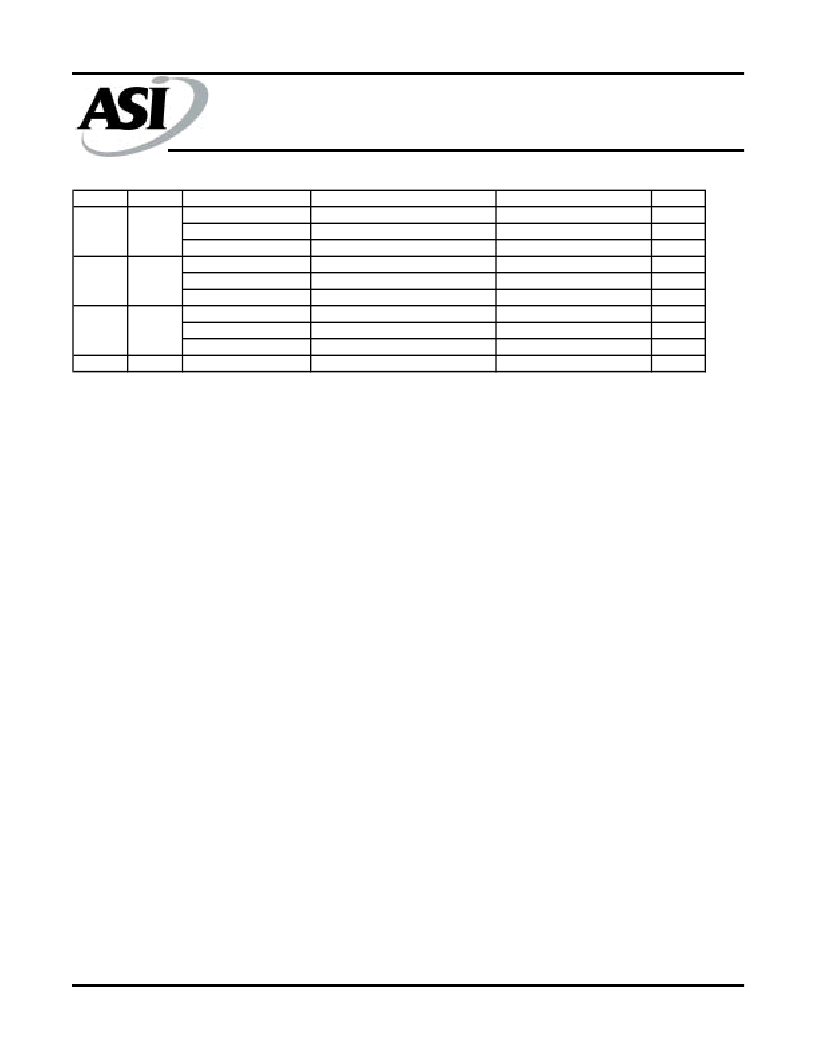

TRUTH TABLE 2: CKE

1,2,3,4

CKEn-1

CKEn

CURRENT STATE

Power-Down

Self Refresh

Clock Suspend

Power-Down

Self Refresh

Clock Suspend

All Banks Idle

All Banks Idle

Reading or Writing

COMMANDn

X

X

X

ACTIONn

NOTES

Maintain Power-Down

Maintain Self Refresh

Maintain Clock Suspend

COMMAND INHIBIT or NOP Exit Power-Down

COMMAND INHIBIT or NOP Exit Self Refresh

X

COMMAND INHIBIT or NOP Power-Down Entry

AUTO REFRESH

VALID

See Truth Table 3

5

6

7

Exit Clock Suspend

Self Refresh Entry

Clock Suspend Entry

H

H

L

L

H

H

L

L

NOTES:

1. CKE

n

is the logic state of CKE at clock edge

n

; CKE

n-1

was the state of CKE at the previous clock edge.

2. Current state is the state of the SDRAM immediately prior to clock edge

n

.

3. COMMAND

n

is the command registered at clock edge

n

, and ACTION

n

is a result of COMMAND

n

.

4. All states and sequences not shown are illegal or reserved.

5. Exiting power-down at clock edge

n

will put the device in the all banks idle state in time for clock edge

n+1

(provided

that t

CKS

is met).

6. Exiting self refresh at clock edge

n

will put the device in the all banks idle state once t

XSR

is met. COMMAND INHIBIT or NOP

commands should be issued on any clock edges occurring during the t

XSR

period. A minimum of two NOP commands must be

provided during t

XSR

period.

7. After exiting clock suspend at clock edge

n

, the device will resume operation and recognize the next command at clock

edge

n+1

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AS5010 | Voltage Reference |

| AS5010GN | Voltage Reference |

| AS5010HN | Voltage Reference |

| AS5010JT | Voltage Reference |

| AS5010KT | Voltage Reference |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AS4SD4M16DG-10/IT | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:4 Meg x 16 SDRAM Synchronous DRAM Memory |

| AS4SD4M16DG-10/XT | 制造商:Micross Components 功能描述:SDRAM-SDR,64MB - Trays |

| AS4SD4M16DG-8/ET | 制造商:Micross Components 功能描述:SDRAM-SDR,64MB - Trays |

| AS4SD4M16DG-8/IT | 制造商:Micross Components 功能描述:SDRAM-SDR,64MB - Trays |

| AS4SD4M16DG-8/XT | 制造商:Micross Components 功能描述:SDRAM-SDR,64MB - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復。