- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366550 > AM79C972BKIW (ADVANCED MICRO DEVICES INC) PCnet⑩-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support PDF資料下載

參數(shù)資料

| 型號(hào): | AM79C972BKIW |

| 廠商: | ADVANCED MICRO DEVICES INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | PCnet⑩-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support |

| 中文描述: | 5 CHANNEL(S), 100M bps, LOCAL AREA NETWORK CONTROLLER, PQFP16 |

| 封裝: | PLASTIC, QFP-160 |

| 文件頁(yè)數(shù): | 93/130頁(yè) |

| 文件大?。?/td> | 1580K |

| 代理商: | AM79C972BKIW |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)當(dāng)前第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)

Am79C972

93

order for the receiver to accept unicast frames directed

to this station.

The six bytes of the IEEE station address occupy the

first six locations of the Address PROM space. The

next six bytes are reserved. Bytes 12 and 13 should

match the value of the checksum of bytes 1 through 11

and 14 and 15. Bytes 14 and 15 should each be ASCII

“

W

”

(57h). The above requirements must be met in

order to be compatible with AMD driver software.

APROMWE bit (BCR2, bit 8) must be set to 1 to enable

write access to the Address PROM space.

Reset Register

A read of the Reset register creates an internal soft-

ware reset (S_RESET) pulse in the Am79C972 control-

ler. The internal S_RESET pulse that is generated by

this access is different from both the assertion of the

hardware RST pin (H_RESET) and from the assertion

of the software STOP bit. Specifically, S_RESET is the

equivalent of the assertion of the RST pin (H_RESET)

except that S_RESET has no effect on the BCR or PCI

Configuration space locations.

The NE2100 LANCE-based family of Ethernet cards

requires that a write access to the Reset register fol-

lows each read access to the Reset register. The

Am79C972 controller does not have a similar require-

ment. The write access is not required and does not

have any effect.

Note:

The Am79C972 controller cannot service any

slave accesses for a very short time after a read access

of the Reset register, because the internal S_RESET

operation takes about 1

μ

s to finish. The Am79C972

controller will terminate all slave accesses with the as-

sertion of DEVSEL and STOP while TRDY is not as-

serted, signaling to the initiator to disconnect and retry

the access at a later time.

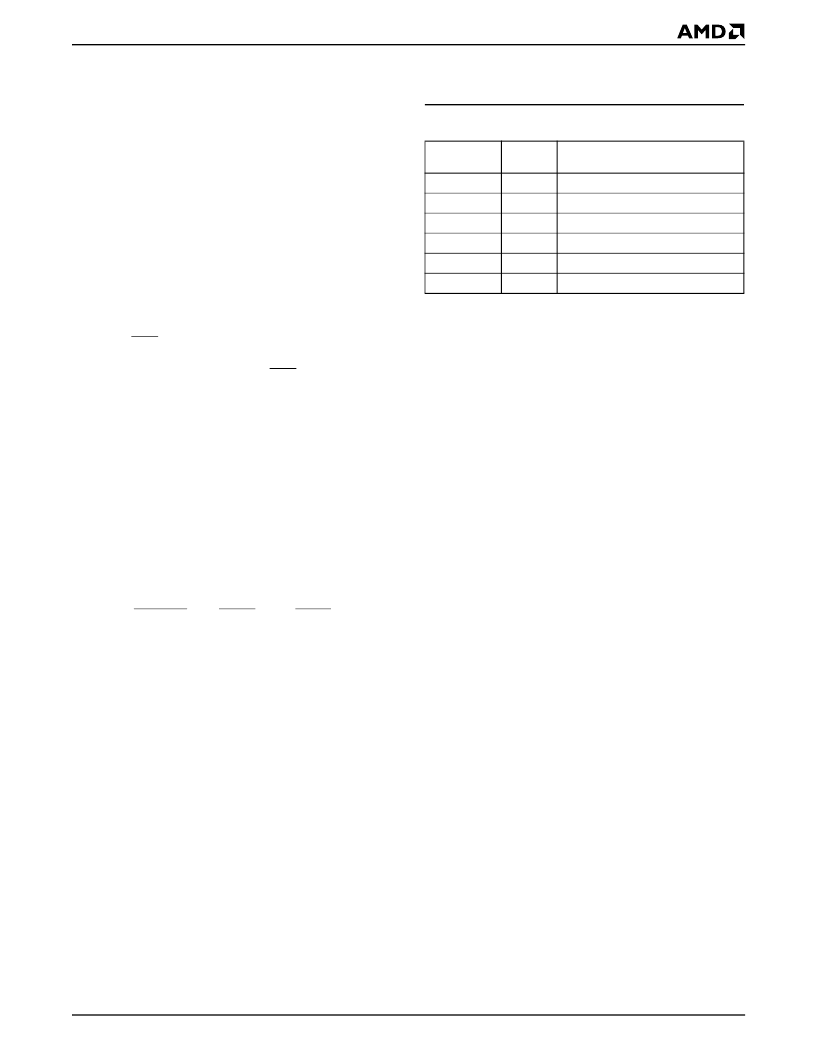

Word I/O Mode

After H_RESET, the Am79C972 controller is pro-

grammed to operate in Word I/O mode. DWIO (BCR18,

bit 7) will be cleared to 0. Table 17 shows how the 32

bytes of address space are used in Word I/O mode.

All I/O resources must be accessed in word quantities

and on word addresses. The Address PROM locations

can also be read in byte quantities. The only allowed

DWord operation is a write access to the RDP, which

switches the device to DWord I/O mode. A read access

other than listed in the table below will yield undefined

data, a write operation may cause unexpected repro-

gramming of the Am79C972 control registers. Table 18

shows legal I/O accesses in Word I/O mode.

Double Word I/O Mode

The Am79C972 controller can be configured to operate

in DWord (32-bit) I/O mode. The software can invoke

the DWIO mode by performing a DWord write access

to the I/O location at offset 10h (RDP). The data of the

write access must be such that it does not affect the in-

tended operation of the Am79C972 controller. Setting

the device into 32-bit I/O mode is usually the first oper-

ation after H_RESET or S_RESET. The RAP register

will point to CSR0 at that time. Writing a value of 0 to

CSR0 is a safe operation. DWIO (BCR18, bit 7) will be

set to 1 as an indication that the Am79C972 controller

operates in 32-bit I/O mode.

Note:

Even though the I/O resource mapping changes

when the I/O mode setting changes, the RDP location

offset is the same for both modes. Once the DWIO bit

has been set to 1, only H_RESET can clear it to 0. The

DWIO mode setting is unaffected by S_RESET or set-

ting of the STOP bit. Table 19 shows how the 32 bytes

of address space are used in DWord I/O mode.

All I/O resources must be accessed in DWord quanti-

ties and on DWord addresses. A read access other

than listed in Table 20 will yield undefined data, a write

operation may cause unexpected reprogramming of

the Am79C972 control registers.

Table 17.

I/O Map In Word I/O Mode (DWIO = 0)

No. of

Bytes

16

2

2

RAP (shared by RDP and BDP)

2

Reset Register

2

8

Offset

00h - 0Fh

10h

12h

14h

16h

18h - 1Fh

Register

APROM

RDP

BDP

Reserved

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM79C972BVCW | PCnet⑩-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support |

| AM79C972 | PCnet⑩-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support |

| AM79C972BVIW | PCnet⑩-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support |

| AM79C974 | PCnetTM-SCSI Combination Ethernet and SCSI Controller for PCI Systems |

| AM79C974KCW | PCnetTM-SCSI Combination Ethernet and SCSI Controller for PCI Systems |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM79C972BVC | 制造商:Advanced Micro Devices 功能描述: |

| AM79C972BVC\W | 制造商:Advanced Micro Devices 功能描述:Ethernet CTLR Single Chip 10Mbps/100Mbps 3.3V 176-Pin TQFP Tray 制造商:Advanced Micro Devices 功能描述:5 CHANNEL(S), 100M bps, LOCAL AREA NETWORK CONTROLLER, PQFP176 |

| AM79C972BVCW | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnet⑩-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support |

| AM79C972BVD\\W | 制造商:Advanced Micro Devices 功能描述: |

| AM79C972BVD\W | 制造商:Advanced Micro Devices 功能描述:Ethernet CTLR Single Chip 10Mbps/100Mbps 3.3V 176-Pin TQFP Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。