- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366550 > AM79C972BKIW (ADVANCED MICRO DEVICES INC) PCnet⑩-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support PDF資料下載

參數(shù)資料

| 型號: | AM79C972BKIW |

| 廠商: | ADVANCED MICRO DEVICES INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | PCnet⑩-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support |

| 中文描述: | 5 CHANNEL(S), 100M bps, LOCAL AREA NETWORK CONTROLLER, PQFP16 |

| 封裝: | PLASTIC, QFP-160 |

| 文件頁數(shù): | 49/130頁 |

| 文件大小: | 1580K |

| 代理商: | AM79C972BKIW |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁當(dāng)前第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁

Am79C972

49

Burst FIFO DMA Transfers

Bursting is only performed by the Am79C972 controller

if the BREADE and/or BWRITE bits of BCR18 are set.

These bits individually enable/disable the ability of the

Am79C972 controller to perform burst accesses during

master read operations and master write operations,

respectively.

A burst transaction will start with an address phase, fol-

lowed by one or more data phases. AD[1:0] will always

be 0 during the address phase indicating a linear burst

order.

During FIFO DMA read operations, all byte lanes will

always be active. The Am79C972 controller will inter-

nally discard unused bytes. During the first and the last

data phases of a FIFO DMA burst write operation, one

or more of the byte enable signals may be inactive. All

other data phases will always write a complete DWord.

Figure 29 shows the beginning of a FIFO DMA write

with the beginning of the buffer not aligned to a DWord

boundary. The Am79C972 controller starts off by writ-

ing only three bytes during the first data phase. This op-

eration aligns the address for all other data transfers to

a 32-bit boundary so that the Am79C972 controller can

continue bursting full DWords.

If a receive buffer does not end on a DWord boundary,

the Am79C972 controller will perform a non-DWord

write on the last transfer to the buffer. Figure 30 shows

the final three FIFO DMA transfers to a receive buffer.

Since there were only nine bytes of space left in the re-

ceive buffer, the Am79C972 controller bursts three data

phases. The first two data phases write a full DWord,

the last one only writes a single byte.

Note that the Am79C972 controller will always perform

a DWord transfer as long as it owns the buffer space,

even when there are less than four bytes to write. For

example, if there is only one byte left for the current re-

ceive frame, the Am79C972 controller will write a full

DWord, containing the last byte of the receive frame in

the least significant byte position (BSWP is cleared to

0, CSR3, bit 2). The content of the other three bytes is

undefined. The message byte count in the receive de-

scriptor always reflects the exact length of the received

frame.

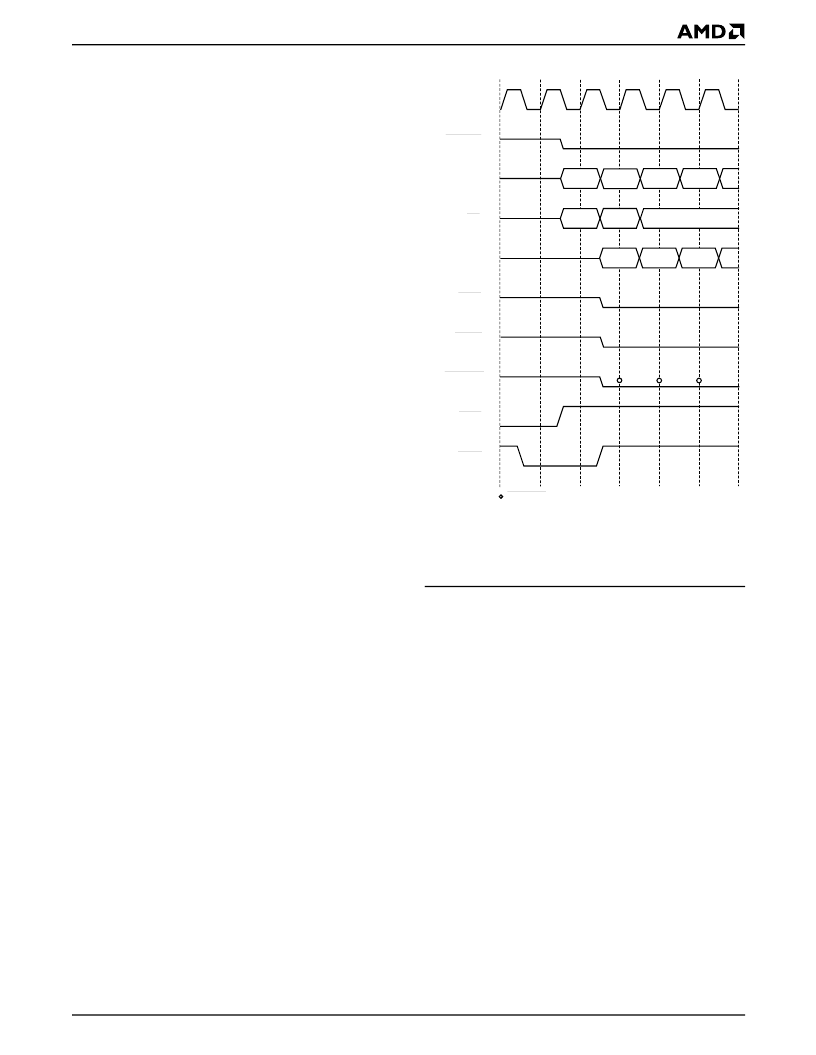

Figure 29.

FIFO Burst Write At Start Of Unaligned

Buffer

The Am79C972 controller will continue transferring

FIFO data until the transmit FIFO is filled to its high

threshold (read transfers) or the receive FIFO is emp-

tied to its low threshold (write transfers), or the

Am79C972 controller is preempted, and the PCI La-

tency Timer is expired. The host should use the values

in the PCI MIN_GNT and MAX_LAT registers to deter-

mine the value for the PCI Latency Timer.

FRAME

CLK

AD

IRDY

TRDY

C/BE

DEVSEL

REQ

GNT

1

2

3

4

5

6

0000

0111

PAR

PAR

PAR

DEVSEL is sampled

0001

PAR

DATA

DATA

DATA

ADD

21485C-32

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM79C972BVCW | PCnet⑩-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support |

| AM79C972 | PCnet⑩-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support |

| AM79C972BVIW | PCnet⑩-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support |

| AM79C974 | PCnetTM-SCSI Combination Ethernet and SCSI Controller for PCI Systems |

| AM79C974KCW | PCnetTM-SCSI Combination Ethernet and SCSI Controller for PCI Systems |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM79C972BVC | 制造商:Advanced Micro Devices 功能描述: |

| AM79C972BVC\W | 制造商:Advanced Micro Devices 功能描述:Ethernet CTLR Single Chip 10Mbps/100Mbps 3.3V 176-Pin TQFP Tray 制造商:Advanced Micro Devices 功能描述:5 CHANNEL(S), 100M bps, LOCAL AREA NETWORK CONTROLLER, PQFP176 |

| AM79C972BVCW | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnet⑩-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support |

| AM79C972BVD\\W | 制造商:Advanced Micro Devices 功能描述: |

| AM79C972BVD\W | 制造商:Advanced Micro Devices 功能描述:Ethernet CTLR Single Chip 10Mbps/100Mbps 3.3V 176-Pin TQFP Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。