- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374034 > ADSP-21366SBSQZENG (ANALOG DEVICES INC) SHARC Processor PDF資料下載

參數(shù)資料

| 型號: | ADSP-21366SBSQZENG |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | SHARC Processor |

| 中文描述: | 16-BIT, 55.55 MHz, OTHER DSP, PQFP144 |

| 封裝: | LEAD FREE, MS-026BFB-HD, HSLQFP-144 |

| 文件頁數(shù): | 43/54頁 |

| 文件大小: | 559K |

| 代理商: | ADSP-21366SBSQZENG |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁當前第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁

ADSP-21365/6

Preliminary Technical Data

Rev. PrA

|

Page 43 of 54

|

September 2004

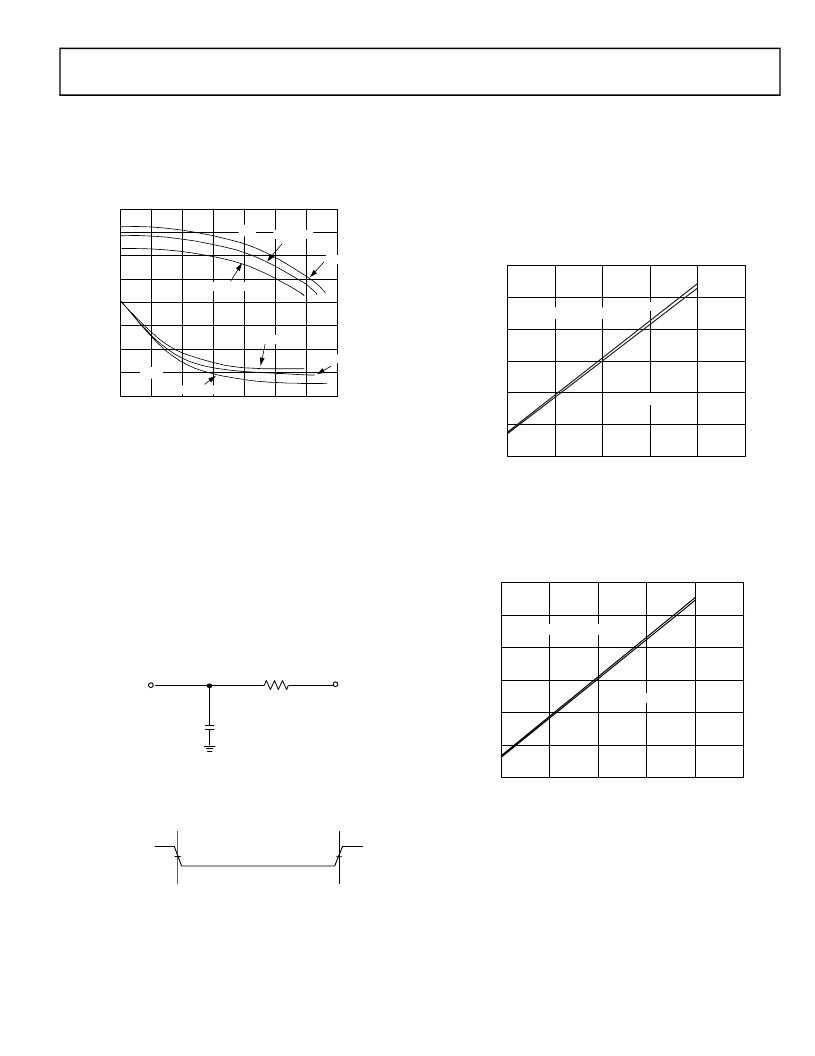

OUTPUT DRIVE CURRENTS

Figure 36

shows typical I-V characteristics for the output driv-

ers of the ADSP-21365/6. The curves represent the current drive

capability of the output drivers as a function of output voltage.

TEST CONDITIONS

The ac signal specifications (timing parameters) appear

Table 12 on page 20

through

Table 38 on page 42

. These include

output disable time, output enable time, and capacitive loading.

The timing specifications for the SHARC apply for the voltage

reference levels in

Figure 37

.

Timing is measured on signals when they cross the 1.5 V level as

described in

Figure 38

. All delays (in nanoseconds) are mea-

sured between the point that the first signal reaches 1.5 V and

the point that the second signal reaches 1.5 V.

CAPACITIVE LOADING

Output delays and holds are based on standard capacitive loads:

30 pF on all pins (see

Figure 37

).

Figure 41

shows graphically

how output delays and holds vary with load capacitance. The

graphs of

Figure 39

,

Figure 40

, and

Figure 41

may not be linear

outside the ranges shown for Typical Output Delay vs. Load

Capacitance and Typical Output Rise Time (20%-80%, V=Min)

vs. Load Capacitance.

Figure 36. ADSP-21365/6 Typical Drive

Figure 37. Equivalent Device Loading for AC Measurements

(Includes All Fixtures)

Figure 38. Voltage Reference Levels for AC Measurements

SWEEP(VDDEXT) VOLTAGE (V)

-20

0

3.5

0.5

1

1.5

2

2.5

3

0

-40

-30

20

40

-10

S

VOL

3.11V, 125° C

3.3V, 25° C

3.47V, -45° C

VOH

30

10

3.11V, 125° C

3.3V, 25° C

3.47V, -45° C

1.5V

30pF

TO

OUTPUT

PIN

50

INPUT

OR

OUTPUT

1.5V

1.5V

Figure 39. Typical Output Rise/Fall Time (20%-80%,

V

DDEXT

= Max)

Figure 40. Typical Output Rise/Fall Time (20%-80%,

V

DDEXT

=Min)

LOAD CAPACITANCE (pF)

8

0

0

100

250

12

4

2

10

6

R

200

150

50

FALL

y = 0.0467x + 1.6323

y = 0.045x + 1.524

RISE

LOAD CAPACITANCE (pF)

12

0

50

100

150

200

250

10

8

6

4

R

2

0

RISE

FALL

y = 0.049x + 1.5105

y = 0.0482x + 1.4604

相關PDF資料 |

PDF描述 |

|---|---|

| ADSP-21366SCSQZENG | SHARC Processor |

| ADSP-21366SKSQ-ENG | SHARC Processor |

| ADSP-21366SBBC-ENG | SHARC Processor |

| ADSP-2164BP-40 | SWITCH PB SPDT VERT .4VA SEALED |

| ADSP-2161BS-66 | DSP Microcomputers with ROM |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| ADSP-21366SCSQ-ENG | 制造商:AD 制造商全稱:Analog Devices 功能描述:SHARC Processor |

| ADSP-21366SCSQZENG | 制造商:AD 制造商全稱:Analog Devices 功能描述:SHARC Processor |

| ADSP-21366SKBC-ENG | 制造商:AD 制造商全稱:Analog Devices 功能描述:SHARC Processor |

| ADSP-21366SKBCZENG | 制造商:AD 制造商全稱:Analog Devices 功能描述:SHARC Processor |

| ADSP-21366SKSQ-ENG | 制造商:AD 制造商全稱:Analog Devices 功能描述:SHARC Processor |

發(fā)布緊急采購,3分鐘左右您將得到回復。