- 您現在的位置:買賣IC網 > PDF目錄374034 > ADSP-21366SBSQZENG (ANALOG DEVICES INC) SHARC Processor PDF資料下載

參數資料

| 型號: | ADSP-21366SBSQZENG |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 數字信號處理 |

| 英文描述: | SHARC Processor |

| 中文描述: | 16-BIT, 55.55 MHz, OTHER DSP, PQFP144 |

| 封裝: | LEAD FREE, MS-026BFB-HD, HSLQFP-144 |

| 文件頁數: | 28/54頁 |

| 文件大?。?/td> | 559K |

| 代理商: | ADSP-21366SBSQZENG |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當前第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁

Rev. PrA

|

Page 28 of 54

|

September 2004

ADSP-21365/6

Preliminary Technical Data

Table 23. 16-bit Memory Write Cycle

Parameter

Switching Characteristics

t

ALEW

t

ADAS

1

t

ALERW

t

RWALE

t

WRH

t

ADAH

1

t

WW

t

ALEHZ

1

t

DWS

t

DWH

D = (Data Cycle Duration = the value set by the PPDUR bits (5–1) in the PPCTL register) × t

PCLK

H = t

PCLK

(if a hold cycle is specified, else H = 0)

F = 7 x t

PCLK

(if FLASH_MODE is set else F = 0)

1

On reset, ALE is an active high cycle. However, it can be configured by software to be active low.

Min

Max

Unit

ALE Pulse Width

Address/Data 15–0 Setup Before ALE Deasserted

ALE Deasserted to Write Asserted

Write Deasserted to ALE Asserted

Delay Between WR Rising Edge to next WR Falling Edge

Address/Data 15–0 Hold After ALE Deasserted

WR Pulse Width

ALE Deasserted to Address/Data15–0 in High Z

Address/Data 15–0 Setup Before WR High

Address/Data 15–0 Hold After WR High

2 × t

PCLK

– 2

t

PCLK

– 2.5

2 × t

PCLK

– 2

H + 0.5

F + H + t

PCLK

– 2

t

PCLK

– 0.5

D – F – 2

t

PCLK

– 1.5

D – F + t

PCLK

– 4

H

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

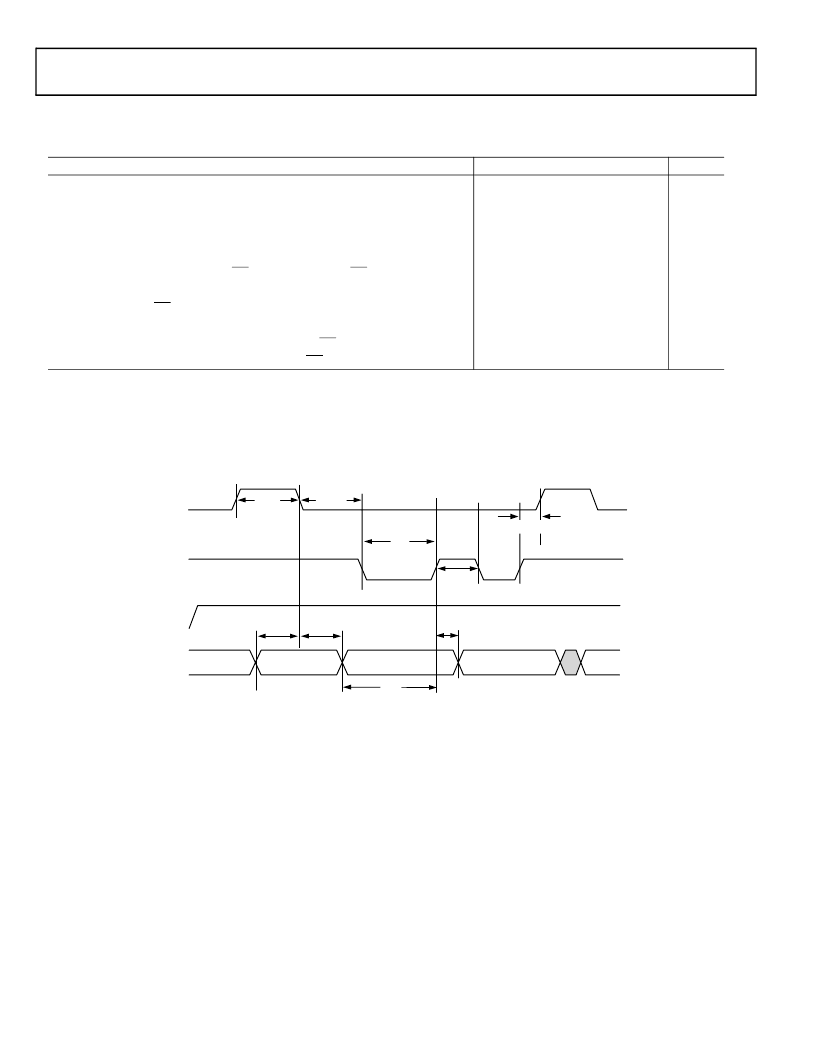

Figure 20. Write Cycle For 16-Bit Memory Timing

AD15-0

VALID

ADDRESS

VALID DATA

t

ADAS

ALE

RD

WR

t

ADAH

t

WRH

t

RWALE

t

ALEW

t

ALERW

t

WW

t

DWS

t

DWH

VALID DATA

相關PDF資料 |

PDF描述 |

|---|---|

| ADSP-21366SCSQZENG | SHARC Processor |

| ADSP-21366SKSQ-ENG | SHARC Processor |

| ADSP-21366SBBC-ENG | SHARC Processor |

| ADSP-2164BP-40 | SWITCH PB SPDT VERT .4VA SEALED |

| ADSP-2161BS-66 | DSP Microcomputers with ROM |

相關代理商/技術參數 |

參數描述 |

|---|---|

| ADSP-21366SCSQ-ENG | 制造商:AD 制造商全稱:Analog Devices 功能描述:SHARC Processor |

| ADSP-21366SCSQZENG | 制造商:AD 制造商全稱:Analog Devices 功能描述:SHARC Processor |

| ADSP-21366SKBC-ENG | 制造商:AD 制造商全稱:Analog Devices 功能描述:SHARC Processor |

| ADSP-21366SKBCZENG | 制造商:AD 制造商全稱:Analog Devices 功能描述:SHARC Processor |

| ADSP-21366SKSQ-ENG | 制造商:AD 制造商全稱:Analog Devices 功能描述:SHARC Processor |

發(fā)布緊急采購,3分鐘左右您將得到回復。