- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1895 > AD9983AKSTZ-170 (Analog Devices Inc)IC DISPLAY 8BIT 170MSPS 80LQFP PDF資料下載

參數(shù)資料

| 型號(hào): | AD9983AKSTZ-170 |

| 廠商: | Analog Devices Inc |

| 文件頁數(shù): | 19/44頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC DISPLAY 8BIT 170MSPS 80LQFP |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 應(yīng)用: | 視頻 |

| 接口: | 模擬 |

| 電源電壓: | 1.7 V ~ 3.47 V |

| 封裝/外殼: | 80-LQFP |

| 供應(yīng)商設(shè)備封裝: | 80-LQFP(14x14) |

| 包裝: | 管件 |

| 安裝類型: | 表面貼裝 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當(dāng)前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁

AD9983A

Rev. 0 | Page 26 of 44

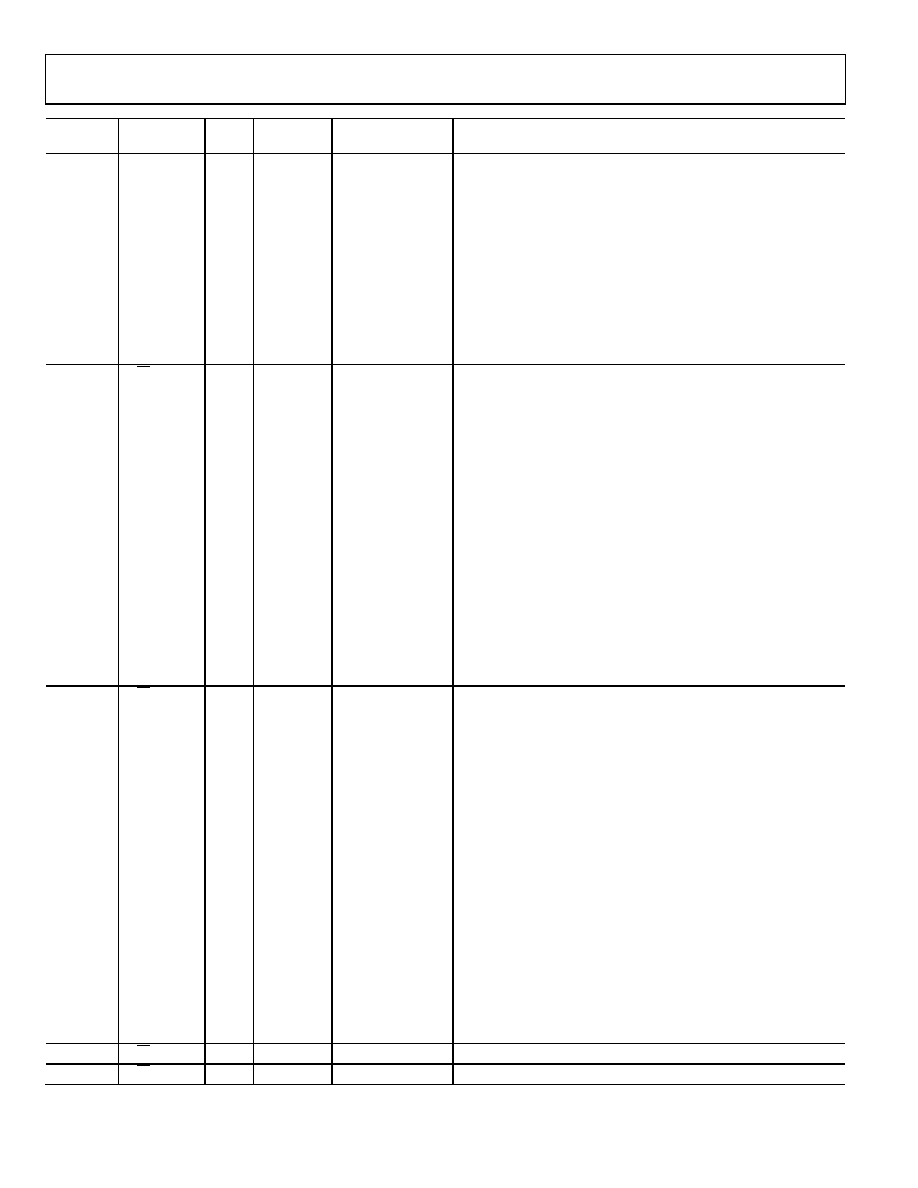

Hex

Address

Read/Write,

Read Only

Bits

Default

Value

Register Name

Description

3

**** 0***

Power-Down.

0 = Normal operation

1 = Power-down

2

**** *0**

Power-Down Pin Polarity.

0 = Active low

1 = Active high

1

**** **0*

Power-Down Fast Switching Control.

0 = Normal power-down operation

1 = The chip stays powered up and the outputs are put in high

impedance mode

0

**** ***0

SOGOUT High Impedance Control.

0 = SOGOUT operates as normal during power-down

1 = SOGOUT is in high impedance during power-down

0x1F

R/W

7:5

100* ****

Output Select 1

Output Mode.

100 = 4:4:4 output mode

101 = 4:2:2 output mode

110 = 4:4:4—DDR output mode

4

***1 ****

Primary Output Enable.

0 = Primary output is in high impedance state

1 = Primary output is enabled

3

**** 0***

Secondary Output Enable.

0 = Secondary output is in high impedance state

1 = Secondary output is enabled

2:1

**** *10*

Output Drive Strength.

00 = Low output drive strength

01 = Medium output drive strength

10 = High output drive strength

11 = High output drive strength

Applies to all outputs except VSOUT.

0

**** ***0

Output Clock Invert.

0 = Noninverted pixel clock

1 = Inverted pixel clock

Applies to all clocks output on DATACK.

0x20

R/W

7:6

0*** ****

Output Select 2

Output Clock Select.

00 = Pixel clock

01 = 90° phase shifted pixel clock

10 = 2× pixel clock

11 = 0.5× pixel clock

5

*0** ****

Output High Impedance.

0 = Normal outputs

1 = All outputs except SOGOUT in high impedance mode

4

**0* ****

SOG High Impedance.

0 = Normal SOG output

1 = SOGOUT pin is in high impedance mode

3

***0 ****

Field Output Polarity. Sets the polarity of the field output signal.

0 = Active low => even field, active high => odd field

1 = Active low => odd field, active high => even field

2

**** 1***

PLL Sync Filter Enable.

0 = PLL uses raw Hsync/SOG

1 = PLL uses filtered Hsync/SOG

1

**** *0**

Sync Processing Input Select. Selects the sync source for the sync

processor.

0 = Sync processing uses raw Hsync/SOGIN

1 = Sync processing uses regenerated Hsync from sync filter

0

Must be set to 1 for proper operation.

0x21

R/W

7:0

0010 0000

Must be set to default for proper operation.

0x22

R/W

7:0

0011 0010

Must be set to default for proper operation.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD9985KSTZ-140 | IC INTERFACE 8BIT 140MSPS 80LQFP |

| AD9990BBCZ | IC CCD SGNL PROCESSOR 112CSPBGA |

| AD9991KCPZRL | IC CCD SIGNAL PROCESSOR 56-LFCSP |

| AD9992BBCZRL | IC CCD SGNL PROC 12BIT 105CSPBGA |

| AD9995KCPZ | IC CCD SIGNAL PROCESSOR 56-LFCSP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9983AKSTZ-1701 | 制造商:AD 制造商全稱:Analog Devices 功能描述:High Performance 8-Bit Display Interface |

| AD9983KSTZ-110 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述: |

| AD9983KSTZ-140 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Analog Devices 功能描述: |

| AD9983KSTZ-170 | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Analog Devices 功能描述: |

| AD9984A | 制造商:AD 制造商全稱:Analog Devices 功能描述:High Performance 10-Bit Display Interface |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。