- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361237 > Q67100-Q2064 (SIEMENS AG) 1M x 32-Bit Dynamic RAM Module PDF資料下載

參數(shù)資料

| 型號(hào): | Q67100-Q2064 |

| 廠商: | SIEMENS AG |

| 英文描述: | 1M x 32-Bit Dynamic RAM Module |

| 中文描述: | 100萬× 32位動(dòng)態(tài)隨機(jī)存儲(chǔ)器模塊 |

| 文件頁數(shù): | 39/53頁 |

| 文件大小: | 418K |

| 代理商: | Q67100-Q2064 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁當(dāng)前第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁

HYB39S64400/800/160BT(L)

64MBit Synchronous DRAM

Semiconductor Group

38

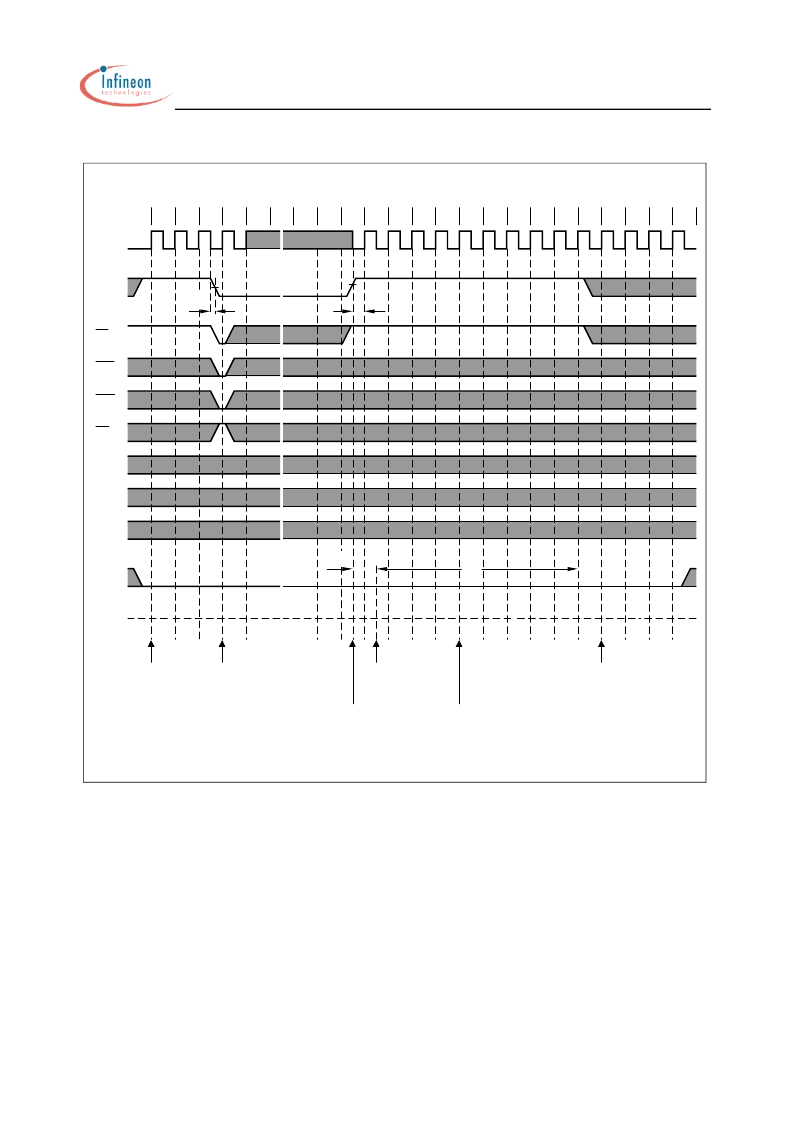

14. Self Refresh (Entry and Exit)

BS

t

Self Refresh Exit

Command issued

Addr.

DQM

DQ

AP

Entry

Self Refresh

must be idle

All Banks

Hi-Z

~

~

~

~

~

~

~

SPT03919

Exit Command

Begin Self Refresh

SREX

t

RC

Self Refresh

Exit

Command

Any

T7

CS

CAS

WE

RAS

CKE

CLK

~

~

~

~

~

~

~

~

t

CKS

T0

T1

T2

~

~

T3

T4

~

~

T6

T5

T16

CKS

t

T8

T9

T10

T11

T14

T12

T13

T15

T18

T17

T19

T20

T21 T22

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| Q67100-Q2065 | 1M x 32-Bit Dynamic RAM Module |

| Q67100-Q2066 | 2M x 32-Bit Dynamic RAM Module |

| Q67100-Q2149 | 3.3V 256 K x 16-Bit EDO-DRAM 3.3V 256 K x 16-Bit EDO-DRAM Low power version with Self Refresh |

| Q67100-Q2156 | 4M x 32-Bit EDO-DRAM Module |

| Q67100-Q2157 | 4M x 32-Bit EDO-DRAM Module |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| Q67100-Q2065 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:1M x 32-Bit Dynamic RAM Module |

| Q67100-Q2066 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:2M x 32-Bit Dynamic RAM Module |

| Q67100-Q2067 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:2M x 32-Bit Dynamic RAM Module |

| Q67100-Q2068 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:2M x 32-Bit Dynamic RAM Module |

| Q67100-Q2069 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:2M x 32-Bit Dynamic RAM Module |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。