- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373891 > AD6655BCPZ-801 (Analog Devices, Inc.) IF Diversity Receiver PDF資料下載

參數(shù)資料

| 型號: | AD6655BCPZ-801 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | IF Diversity Receiver |

| 中文描述: | IF分集接收機 |

| 文件頁數(shù): | 13/84頁 |

| 文件大?。?/td> | 2012K |

| 代理商: | AD6655BCPZ-801 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當(dāng)前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁

AD6655

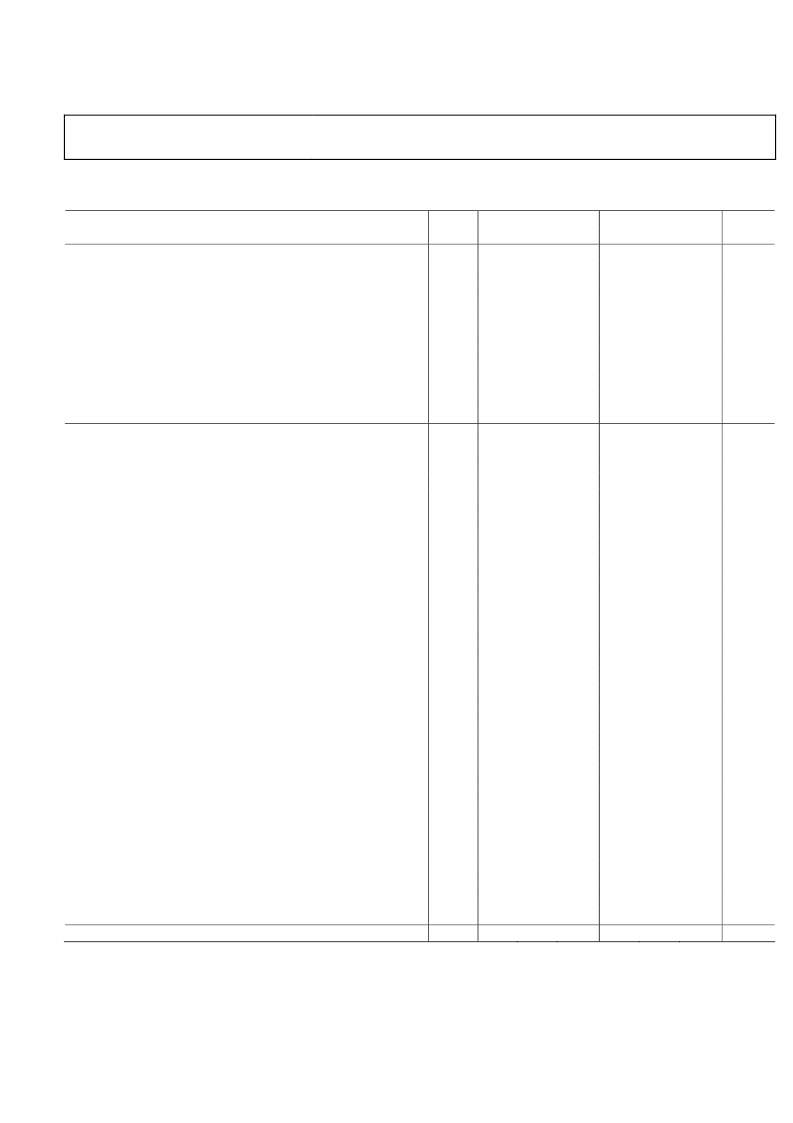

SWITCHING SPECIFICATIONS—AD6655BCPZ-80/AD6655BCPZ-105

Table 7.

Rev. 0 | Page 13 of 84

AD6655BCPZ-80

Min

Typ

20

10

12.5

3.75

6.25

5.63

6.25

1.6

0.8

1.6

3.9

4.0

5.4

14.0

11.0

1.9

4.1

4.4

5.8

14.2

10.8

1.6

3.9

3.4

4.8

7.15

5.35

1.9

4.1

3.8

5.2

7.35

5.15

2.5

4.8

3.7

5.3

38

38

AD6655BCPZ-105

Min

Typ

20

10

9.5

2.85

4.75

4.28

4.75

1.6

0.8

1.6

3.9

4.0

5.4

11.0

8.0

1.9

4.1

4.4

5.8

11.2

7.8

1.6

3.9

3.4

4.8

5.65

3.85

1.9

4.1

3.8

5.2

5.85

3.65

2.5

4.8

3.7

5.3

38

38

Parameter

CLOCK INPUT PARAMETERS

Input Clock Rate

Conversion Rate

1

DCS Enabled

DCS Disabled

CLK Period—Divide-by-1 Mode (t

CLK

)

CLK Pulse Width High

(t

CLKH

)

Divide-by-1 Mode, DCS Enabled

Divide-by-1 Mode DCS Disabled

Divide-by-2 Mode, DCS Enabled

Divide-by-3 Through Divide-by-8 Modes, DCS Enabled

DATA OUTPUT PARAMETERS (DATA, FD)

CMOS Noninterleaved Mode—DRVDD = 1.8 V

Data Propagation Delay (t

PD

)

2

DCO Propagation Delay (t

DCO

)

Setup Time (t

S

)

Hold Time (t

H

)

CMOS Noninterleaved Mode—DRVDD = 3.3 V

Data Propagation Delay (t

PD

)

2

DCO Propagation Delay (t

DCO

)

Setup Time (t

S

)

Hold Time (t

H

)

CMOS Interleaved and IQ Mode—DRVDD = 1.8 V

Data Propagation Delay (t

PD

)

2

DCO Propagation Delay (t

DCO

)

Setup Time (t

S

)

Hold Time (t

H

)

CMOS Interleaved and IQ Mode—DRVDD = 3.3 V

Data Propagation Delay (t

PD

)

2

DCO Propagation Delay (t

DCO

)

Setup Time (t

S

)

Hold Time (t

H

)

LVDS Mode—DRVDD = 1.8 V

Data Propagation Delay (t

PD

)

2

DCO Propagation Delay (t

DCO

)

Pipeline Delay (Latency) NCO, FIR, f

S

/8 Mix Disabled

Pipeline Delay (Latency) NCO Enabled, FIR and f

S

/8 Mix Disabled

(Complex Output Mode)

Pipeline Delay (Latency) NCO, FIR, and f

S

/8 Mix Enabled

Aperture Delay (t

A

)

Aperture Uncertainty (Jitter, t

J

)

Wake-Up Time

3

OUT-OF-RANGE RECOVERY TIME

1

Conversion rate is the clock rate after the divider.

2

Output propagation delay is measured from CLK 50% transition to DATA 50% transition, with a 5 pF load.

3

Wake-up time is dependent on the value of the decoupling capacitors.

Temp

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Full

Max

625

80

80

8.75

6.88

6.2

7.3

6.4

7.7

6.2

6.7

6.4

7.1

7.0

7.3

Max

625

105

105

6.65

5.23

6.2

7.3

6.4

7.7

6.2

6.7

6.4

7.1

7.0

7.3

Unit

MHz

MSPS

MSPS

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Cycles

Cycles

Full

Full

Full

Full

Full

109

1.0

0.1

350

2

109

1.0

0.1

350

2

Cycles

ns

ps rms

us

Cycles

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD667JN | Microprocessor-Compatible 12-Bit D/A Converter |

| AD667JP | Microprocessor-Compatible 12-Bit D/A Converter |

| AD667KN | Microprocessor-Compatible 12-Bit D/A Converter |

| AD667KP | Microprocessor-Compatible 12-Bit D/A Converter |

| AD668A | 12-Bit Ultrahigh Speed Multiplying D/A Converter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD6655BCPZRL7-125 | 制造商:Analog Devices 功能描述: |

| AD6655BCPZRL7-150 | 制造商:Analog Devices 功能描述: 制造商:Rochester Electronics LLC 功能描述: |

| AD6657 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Quad IF Receiver |

| AD6657A | 制造商:AD 制造商全稱:Analog Devices 功能描述:Quad IF Receiver |

| AD6657ABBCZ | 功能描述:IC QUAD IF RECEIVER 144BGA RoHS:是 類別:RF/IF 和 RFID >> RF 其它 IC 和模塊 系列:- 標(biāo)準(zhǔn)包裝:100 系列:* |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。