- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄4500 > A54SX08A-FFG144 (Microsemi SoC)IC FPGA SX 12K GATES 144-FBGA PDF資料下載

參數(shù)資料

| 型號(hào): | A54SX08A-FFG144 |

| 廠商: | Microsemi SoC |

| 文件頁(yè)數(shù): | 65/108頁(yè) |

| 文件大小: | 0K |

| 描述: | IC FPGA SX 12K GATES 144-FBGA |

| 標(biāo)準(zhǔn)包裝: | 160 |

| 系列: | SX-A |

| LAB/CLB數(shù): | 768 |

| 輸入/輸出數(shù): | 111 |

| 門(mén)數(shù): | 12000 |

| 電源電壓: | 2.25 V ~ 5.25 V |

| 安裝類(lèi)型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 70°C |

| 封裝/外殼: | 144-LBGA |

| 供應(yīng)商設(shè)備封裝: | 144-FPBGA(13x13) |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)當(dāng)前第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)

SX-A Family FPGAs

1- 2

v5.3

Logic Module Design

The SX-A family architecture is described as a “sea-of-

modules” architecture because the entire floor of the

device is covered with a grid of logic modules with

virtually no chip area lost to interconnect elements or

routing. The Actel SX-A family provides two types of

logic

modules:

the

register

cell

(R-cell)

and

the

combinatorial cell (C-cell).

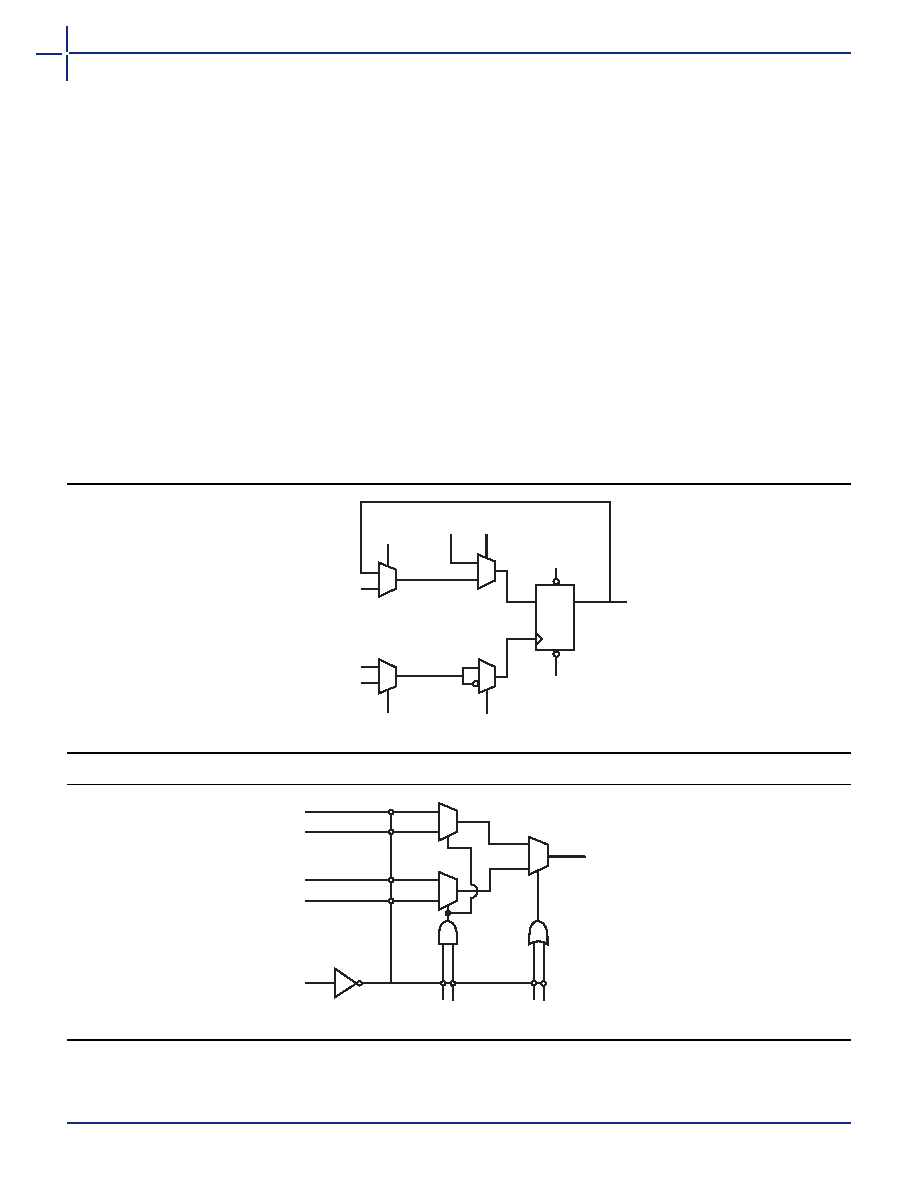

The R-cell contains a flip-flop featuring asynchronous clear,

asynchronous preset, and clock enable, using the S0 and S1

lines control signals (Figure 1-2). The R-cell registers feature

programmable clock polarity selectable on a register-by-

register basis. This provides additional flexibility while

allowing mapping of synthesized functions into the SX-A

FPGA. The clock source for the R-cell can be chosen from

either the hardwired clock, the routed clocks, or internal

logic.

The C-cell implements a range of combinatorial functions

of up to five inputs (Figure 1-3). Inclusion of the DB input

and its associated inverter function allows up to 4,000

different combinatorial functions to be implemented in a

single module. An example of the flexibility enabled by

the inversion capability is the ability to integrate a 3-input

exclusive-OR function into a single C-cell. This facilitates

construction of 9-bit parity-tree functions with 1.9 ns

propagation delays.

Module Organization

All C-cell and R-cell logic modules are arranged into

horizontal banks called Clusters. There are two types of

Clusters: Type 1 contains two C-cells and one R-cell, while

Type 2 contains one C-cell and two R-cells.

Clusters

are

grouped

together

into

SuperClusters

(Figure 1-4 on page 1-3). SuperCluster 1 is a two-wide

grouping of Type 1 Clusters. SuperCluster 2 is a two-wide

group containing one Type 1 Cluster and one Type 2

Cluster. SX-A devices feature more SuperCluster 1

modules than SuperCluster 2 modules because designers

typically require significantly more combinatorial logic

than flip-flops.

Figure 1-2 R-Cell

Figure 1-3 C-Cell

DQ

DirectConnect

Input

CLKA,

CLKB,

Internal Logic

HCLK

CKS

CKP

CLR

PRE

Y

Routed

Data Input

S0

S1

D0

D1

D2

D3

DB

A0 B0

A1 B1

Sa

Sb

Y

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RGM43DTMT | CONN EDGECARD 86POS R/A .156 SLD |

| M1A3P600-1PQG208 | IC FPGA 1KB FLASH 600K 208-PQFP |

| A3P600-1PQG208 | IC FPGA 1KB FLASH 600K 208-PQFP |

| M1A3P600L-PQG208 | IC FPGA 1KB FLASH 600K 208-PQFP |

| A40MX04-PL68I | IC FPGA MX SGL CHIP 6K 68-PLCC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| A54SX08A-FFG208 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:SX-A Family FPGAs |

| A54SX08A-FFG208A | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:SX-A Family FPGAs |

| A54SX08A-FFG208B | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:SX-A Family FPGAs |

| A54SX08A-FFG208I | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:SX-A Family FPGAs |

| A54SX08A-FFG208M | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:SX-A Family FPGAs |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。