- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄4500 > A54SX08A-FFG144 (Microsemi SoC)IC FPGA SX 12K GATES 144-FBGA PDF資料下載

參數(shù)資料

| 型號(hào): | A54SX08A-FFG144 |

| 廠商: | Microsemi SoC |

| 文件頁(yè)數(shù): | 13/108頁(yè) |

| 文件大小: | 0K |

| 描述: | IC FPGA SX 12K GATES 144-FBGA |

| 標(biāo)準(zhǔn)包裝: | 160 |

| 系列: | SX-A |

| LAB/CLB數(shù): | 768 |

| 輸入/輸出數(shù): | 111 |

| 門(mén)數(shù): | 12000 |

| 電源電壓: | 2.25 V ~ 5.25 V |

| 安裝類(lèi)型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 70°C |

| 封裝/外殼: | 144-LBGA |

| 供應(yīng)商設(shè)備封裝: | 144-FPBGA(13x13) |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)當(dāng)前第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)

SX-A Family FPGAs

1- 8

v5.3

Power-Up/Down and Hot Swapping

SX-A I/Os are configured to be hot-swappable, with the

exception of 3.3 V PCI. During power-up/down (or partial

up/down), all I/Os are tristated. VCCA and VCCI do not

have to be stable during power-up/down, and can be

powered up/down in any order. When the SX-A device is

plugged into an electrically active system, the device will

not degrade the reliability of or cause damage to the

host system. The device’s output pins are driven to a high

impedance state until normal chip operating conditions

which the I/Os behave according to the user’s design for

an SX-A device at room temperature for various ramp-up

rates. The data reported assumes a linear ramp-up

profile to 2.5 V. For more information on power-up and

hot-swapping, refer to the application note, Actel SX-A

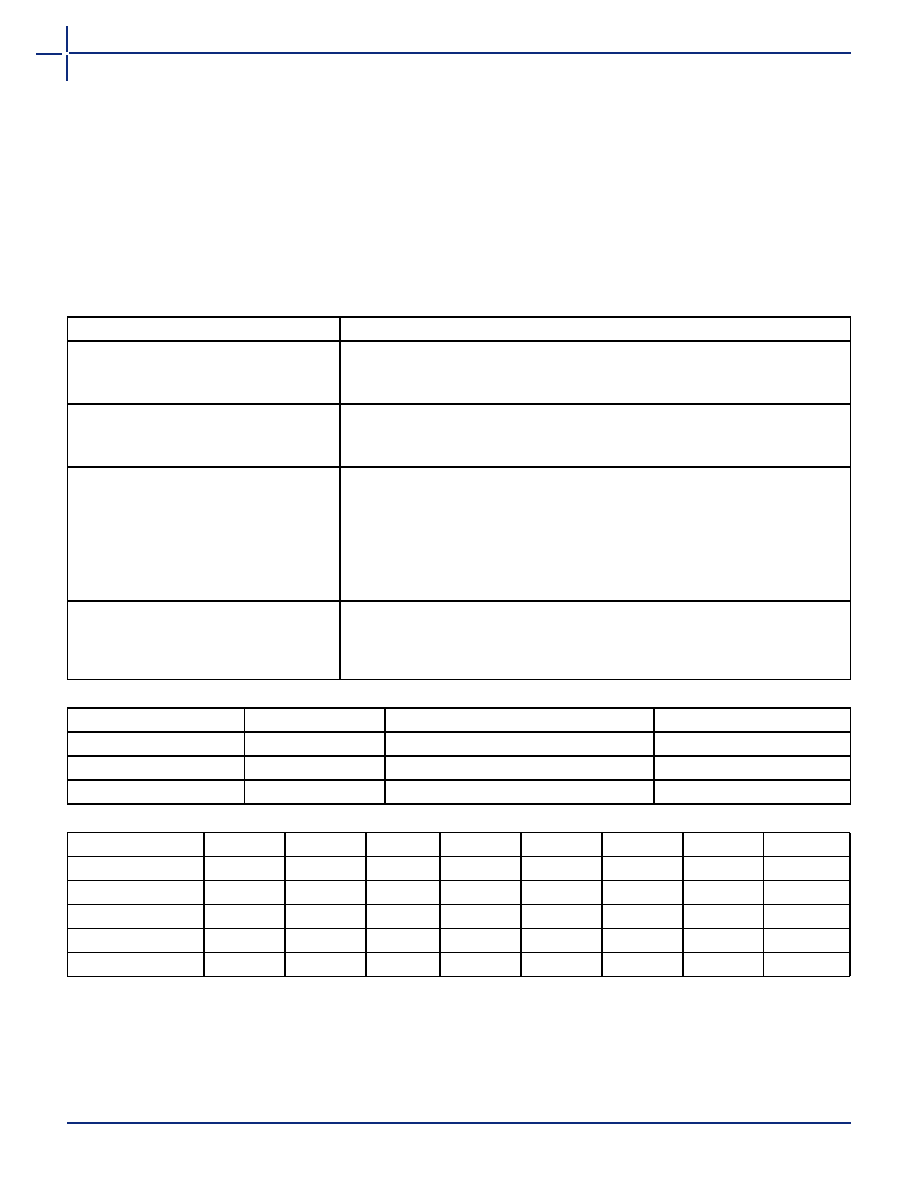

Table 1-2 I/O Features

Function

Description

Input Buffer Threshold Selections

5 V: PCI, TTL

3.3 V: PCI, LVTTL

2.5 V: LVCMOS2 (commercial only)

Flexible Output Driver

5 V: PCI, TTL

3.3 V: PCI, LVTTL

2.5 V: LVCMOS2 (commercial only)

Output Buffer

“Hot-Swap” Capability (3.3 V PCI is not hot swappable)

I/O on an unpowered device does not sink current

Can be used for “cold-sparing”

Selectable on an individual I/O basis

Individually selectable slew rate; high slew or low slew (The default is high slew rate).

The slew is only affected on the falling edge of an output. Rising edges of outputs are

not affected.

Power-Up

Individually selectable pull-ups and pull-downs during power-up (default is to power-up

in tristate)

Enables deterministic power-up of device

VCCA and VCCI can be powered in any order

Table 1-3 I/O Characteristics for All I/O Configurations

Hot Swappable

Slew Rate Control

Power-Up Resistor

TTL, LVTTL, LVCMOS2

Yes

Yes. Only affects falling edges of outputs

Pull-up or pull-down

3.3 V PCI

No

No. High slew rate only

Pull-up or pull-down

5 V PCI

Yes

No. High slew rate only

Pull-up or pull-down

Table 1-4 Power-Up Time at which I/Os Become Active

Supply Ramp Rate

0.25 V/

μs 0.025 V/μs

5 V/ms

2.5 V/ms

0.5 V/ms

0.25 V/ms

0.1 V/ms

0.025 V/ms

Units

μs

ms

msms

ms

A54SX08A

10

96

0.34

0.65

2.7

5.4

12.9

50.8

A54SX16A

10

100

0.36

0.62

2.5

4.7

11.0

41.6

A54SX32A

10

100

0.46

0.74

2.8

5.2

12.1

47.2

A54SX72A

10

100

0.41

0.67

2.6

5.0

12.1

47.2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RGM43DTMT | CONN EDGECARD 86POS R/A .156 SLD |

| M1A3P600-1PQG208 | IC FPGA 1KB FLASH 600K 208-PQFP |

| A3P600-1PQG208 | IC FPGA 1KB FLASH 600K 208-PQFP |

| M1A3P600L-PQG208 | IC FPGA 1KB FLASH 600K 208-PQFP |

| A40MX04-PL68I | IC FPGA MX SGL CHIP 6K 68-PLCC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| A54SX08A-FFG208 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:SX-A Family FPGAs |

| A54SX08A-FFG208A | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:SX-A Family FPGAs |

| A54SX08A-FFG208B | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:SX-A Family FPGAs |

| A54SX08A-FFG208I | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:SX-A Family FPGAs |

| A54SX08A-FFG208M | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:SX-A Family FPGAs |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。