- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25569 > 9LPRS365BKLFT (INTEGRATED DEVICE TECHNOLOGY INC) SPECIALTY MICROPROCESSOR CIRCUIT, PQCC64 PDF資料下載

參數(shù)資料

| 型號: | 9LPRS365BKLFT |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | SPECIALTY MICROPROCESSOR CIRCUIT, PQCC64 |

| 封裝: | PLASTIC, VQFN-64 |

| 文件頁數(shù): | 22/28頁 |

| 文件大小: | 301K |

| 代理商: | 9LPRS365BKLFT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當(dāng)前第22頁第23頁第24頁第25頁第26頁第27頁第28頁

3

ICS9LPRS365

Datasheet

1218—09/01/10

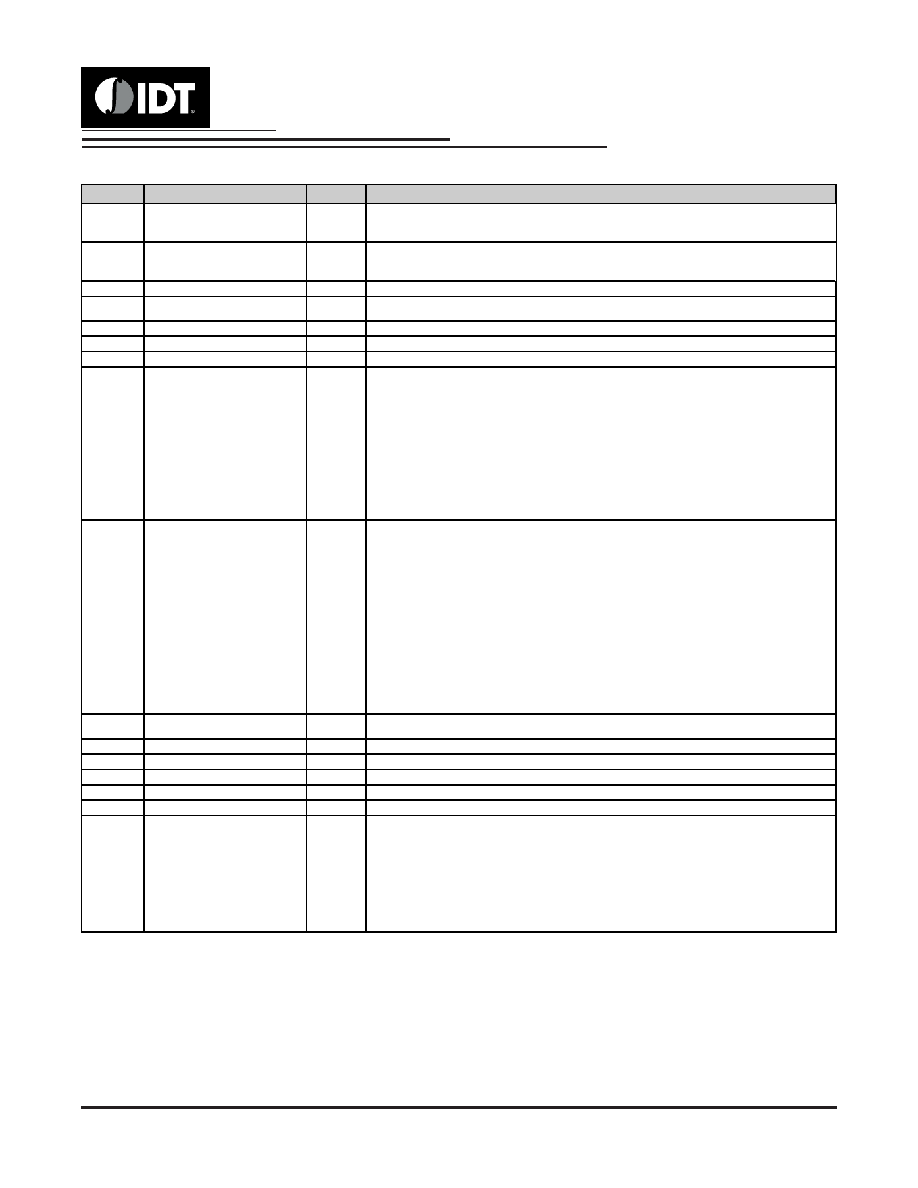

TSSOP Pin Description (Continued)

PIN #

PIN NAME

TYPE

DESCRIPTION

17

27MHz_NonSS/SRCT1/SE1

OUT

True clock of differential SRC1 clock pair / 3.3V single-ended output. 27_Select determines the power-up

default, 1=27MHz non-spread SE clock, 0 = LCD_SST 100MHz differential clock. See table 2 for more

information.

18

27MHz_SS/SRCC1/SE2

OUT

Complement clock of differential SRC1 clock pair / 3.3V single-ended output. 27_Select determines the

power-up default, 1=27MHz spread SE clock, 0 = LCD_SSC 100MHz differential clock. See table 2 for

more information.

19

GND

PWR

Ground pin for SRC / SE1 and SE2 clocks, PLL3.

20

VDDPLL3_IO

PWR

1.05V to 3.3V from external power supply

21

SRCT2/SATAT

OUT

True clock of differential SRC/SATA clock pair.

22

SRCC2/SATAC

OUT

Complement clock of differential SRC/SATA clock pair.

23

GNDSRC

PWR

Ground pin for SRC clocks.

24

SRCT3/CR#_C

I/O

True clock of differential SRC clock pair/ Clock Request control C for either SRC0 or SRC2 pair

The power-up default is SRCCLK3 output, but this pin may also be used as a Clock Request control of

SRC pair 0 or SRC pair 2 via SMBus. Before configuring this pin as a Clock Request Pin, the SRC3 output

must first be disabled in byte 4, bit 7 of SMBus address space . After the SRC3 output is disabled, the pin

can then be set to serve as a Clock Request pin for either SRC pair 2 or pair 0 using the CR#_C_EN bit

located in byte 5 of SMBUs address space.

Byte 5, bit 3

0 = SRC3 enabled (default)

1= CR#_C enabled. Byte 5, bit 2 controls whether CR#_C controls SRC0 or SRC2 pair

Byte 5, bit 2

0 = CR#_C controls SRC0 pair (default),

1= CR#_C controls SRC2 pair

25

SRCC3/CR#_D

I/O

Complementary clock of differential SRC clock pair/ Clock Request control D for either SRC1 or SRC4

pair

The power-up default is SRCCLK3 output, but this pin may also be used as a Clock Request control of

SRC pair 1 or SRC pair 4 via SMBus. Before configuring this pin as a Clock Request Pin, the SRC3 output

must first be disabled in byte 4, bit 7 of SMBus address space . After the SRC3 output is disabled, the pin

can then be set to serve as a Clock Request pin for either SRC pair 1 or pair 4 using the CR#_D_EN bit

located in byte 5 of SMBUs address space.

Byte 5, bit 1

0 = SRC3 enabled (default)

1= CR#_D enabled. Byte 5, bit 0 controls whether CR#_D controls SRC1 or SRC4 pair

Byte 5, bit 0

0 = CR#_D controls SRC1 pair (default),

1= CR#_D controls SRC4 pair

26

VDDSRC_IO

PWR

1.05V to 3.3V from external power supply

27

SRCT4

I/O

True clock of differential SRC clock pair 4

28

SRCC4

I/O

Complement clock of differential SRC clock pair 4

29

GNDSRC

PWR

Ground pin for SRC clocks.

30

SRCT9

OUT

True clock of differential SRC clock pair.

31

SRCC9

OUT

Complement clock of differential SRC clock pair.

32

SRCC11/CR#_G

I/O

SRC11 complement /Clock Request control for SRC9 pair

The power-up default is SRC11#, but this pin may also be used as a Clock Request control of SRC9 via

SMBus. Before configuring this pin as a Clock Request Pin, the SRC11 output pair must first be disabled in

byte 3, bit 7 of SMBus configuration space After the SRC11 output is disabled (high-Z), the pin can then be

set to serve as a Clock Request for SRC9 pair using byte 6, bit 5 of SMBus configuration space

Byte 6, bit 5

0 = SRC11# enabled (default)

1= CR#_G controls SRC9

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 9LPRS365BGLFT | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO64 |

| 9LPRS436CKLF | SPECIALTY MICROPROCESSOR CIRCUIT, PQCC48 |

| 9LPRS436CGLF | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO48 |

| 9LPRS436CKLFT | SPECIALTY MICROPROCESSOR CIRCUIT, PQCC48 |

| 9LPRS436CKILFT | SPECIALTY MICROPROCESSOR CIRCUIT, PQCC48 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 9LPRS387BKLF | 制造商:Integrated Device Technology Inc 功能描述:IDT 9LPRS387BKLF GENERAL PURPOSE SEMICONDUCTORS - Tape and Reel 制造商:Integrated Device Technology Inc 功能描述:IDT 9LPRS387BKLF General Purpose Semiconductors |

| 9LPRS393DKLF | 制造商:Integrated Device Technology Inc 功能描述:IDT 9LPRS393DKLF GENERAL PURPOSE SEMICONDUCTORS - Trays 制造商:Integrated Device Technology Inc 功能描述:IDT 9LPRS393DKLF General Purpose Semiconductors |

| 9LPRS393DKLFT | 制造商:Integrated Device Technology Inc 功能描述:IDT 9LPRS393DKLFT GENERAL PURPOSE SEMICONDUCTORS - Tape and Reel 制造商:Integrated Device Technology Inc 功能描述:IDT 9LPRS393DKLFT General Purpose Semiconductors |

| 9LPRS397DKLF | 制造商:Integrated Device Technology Inc 功能描述:IDT 9LPRS397DKLF GENERAL PURPOSE SEMICONDUCTORS - Trays 制造商:Integrated Device Technology Inc 功能描述:IDT 9LPRS397DKLF General Purpose Semiconductors |

| 9LPRS397DKLFT | 制造商:Integrated Device Technology Inc 功能描述:IDT 9LPRS397DKLFT SEMICONDUCTORS - Tape and Reel 制造商:Integrated Device Technology Inc 功能描述:IDT 9LPRS397DKLFT Semiconductors |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。