- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25569 > 9LPR501YGT (INTEGRATED DEVICE TECHNOLOGY INC) SPECIALTY MICROPROCESSOR CIRCUIT, PDSO64 PDF資料下載

參數(shù)資料

| 型號: | 9LPR501YGT |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO64 |

| 封裝: | 6.10 MM, 0.50 MM PITCH, MO-153, TSSOP-64 |

| 文件頁數(shù): | 2/22頁 |

| 文件大小: | 210K |

| 代理商: | 9LPR501YGT |

IDTTM/ICSTM

64-pin CK505 w/Fully Integrated Voltage Regulator

1118G—02/19/08

Advance Information

ICS9LPR501

64-PIN CK505 W/FULLY INTEGRATED VOLTAGE REGULATOR

10

Datasheet

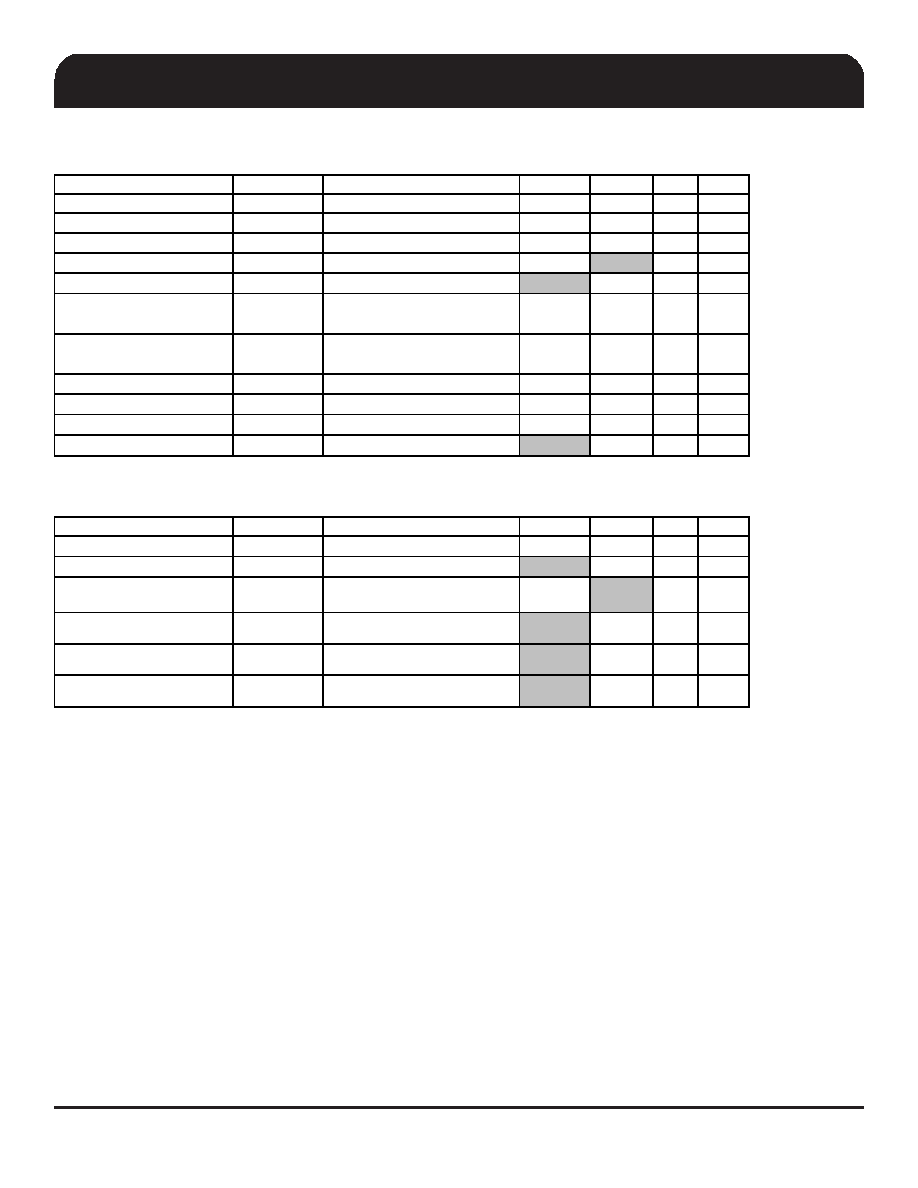

Electrical Characteristics - REF-14.318MHz

PARAMETER

SYMBOL

CONDITIONS

MIN

MAX

UNITS

Notes

Long Accuracy

ppm

see Tperiod min-max values

-300

300

ppm

1,2

Clock period

T

period

14.318MHz output nominal

69.8203

69.8622

ns

2

Absolute min/max period

T

abs

14.318MHz output nominal

69.8203

70.86224

ns

2

Output High Voltage

V

OH

I

OH = -1 mA

2.4

V

1

Output Low Voltage

V

OL

I

OL = 1 mA

0.4

V

1

Output High Current

I

OH

V

OH @MIN = 1.0 V,

V

OH@MAX = 3.135 V

-33

mA

1

Output Low Current

I

OL

V

OL @MIN = 1.95 V,

V

OL @MAX = 0.4 V

30

38

mA

1

Rising Edge Slew Rate

t

SLR

Measured from 0.8 to 2.0 V

1

4

V/ns

1

Falling Edge Slew Rate

t

FLR

Measured from 2.0 to 0.8 V

1

4

V/ns

1

Duty Cycle

d

t1

V

T = 1.5 V

45

55

%

1

Jitter

t

jcyc-cyc

V

T = 1.5 V

1000

ps

1

Electrical Characteristics - SMBus Interface

PARAMETER

SYMBOL

CONDITIONS

MIN

MAX

UNITS

Notes

SMBus Voltage

V

DD

2.7

5.5

V

1

Low-level Output Voltage

V

OLSMB

@ I

PULLUP

0.4

V

1

Current sinking at

V

OLSMB = 0.4 V

I

PULLUP

SMB Data Pin

4

mA

1

SCLK/SDATA

Clock/Data Rise Time

T

RI2C

(Max VIL - 0.15) to

(Min VIH + 0.15)

1000

ns

1

SCLK/SDATA

Clock/Data Fall Time

T

FI2C

(Min VIH + 0.15) to

(Max VIL - 0.15)

300

ns

1

Maximum SMBus Operating

Frequency

F

SMBUS

Block Mode

100

kHz

1

Notes on Electrical Characteristics:

1Guaranteed by design and characterization, not 100% tested in production.

2 Slew rate measured through Vswing centered around differential zero

3 Vxabs is defined as the voltage where CLK = CLK#

4 Only applies to the differential rising edge (CLK rising and CLK# falling)

6 All Long Term Accuracy and Clock Period specifications are guaranteed assuming that REFOUT is at 14.31818MHz

5 Defined as the total variation of all crossing voltages of CLK rising and CLK# falling. Matching applies to rising edge rate of

CLK and falling edge of CLK#. It is measured using a +/-75mV window centered on the average cross point where CLK meets

CLK#. The average cross point is used to calculate the voltage thresholds the oscilloscope is to use for the edge rate

calculations.

7 Operation under these conditions is neither implied, nor guaranteed.

9 See PCI Clock-to-Clock Delay Figure

8 Maximum input voltage is not to exceed maximum VDD

相關PDF資料 |

PDF描述 |

|---|---|

| 9LPR502YGLFT | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO56 |

| 9LPRS365BKLFT | SPECIALTY MICROPROCESSOR CIRCUIT, PQCC64 |

| 9LPRS365BGLFT | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO64 |

| 9LPRS436CKLF | SPECIALTY MICROPROCESSOR CIRCUIT, PQCC48 |

| 9LPRS436CGLF | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO48 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 9LPR502HGLF | 制造商:Integrated Device Technology Inc 功能描述:PC CLOCK, TSSOP56 - Rail/Tube |

| 9LPR502HGLFT | 制造商:Integrated Device Technology Inc 功能描述:PC CLOCK, TSSOP56 - Rail/Tube |

| 9LPR502SGLF | 功能描述:時鐘合成器/抖動清除器 PC MAIN CLOCK RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| 9LPR502SGLFT | 功能描述:時鐘合成器/抖動清除器 PC MAIN CLOCK RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| 9LPR502YFLFT | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:56-PIN CK505 W/FULLY INTEGRATED VOLTAGE REGULATOR |

發(fā)布緊急采購,3分鐘左右您將得到回復。