- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25548 > 97ULP877BHLF-T (INTEGRATED DEVICE TECHNOLOGY INC) 97ULP SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA52 PDF資料下載

參數(shù)資料

| 型號: | 97ULP877BHLF-T |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘及定時 |

| 英文描述: | 97ULP SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA52 |

| 封裝: | LEAD FREE ANNEALED, MO-205, MO-225, BGA-52 |

| 文件頁數(shù): | 3/14頁 |

| 文件大小: | 179K |

| 代理商: | 97ULP877BHLF-T |

11

ICS97ULP8 77B

0981C—04/05/05

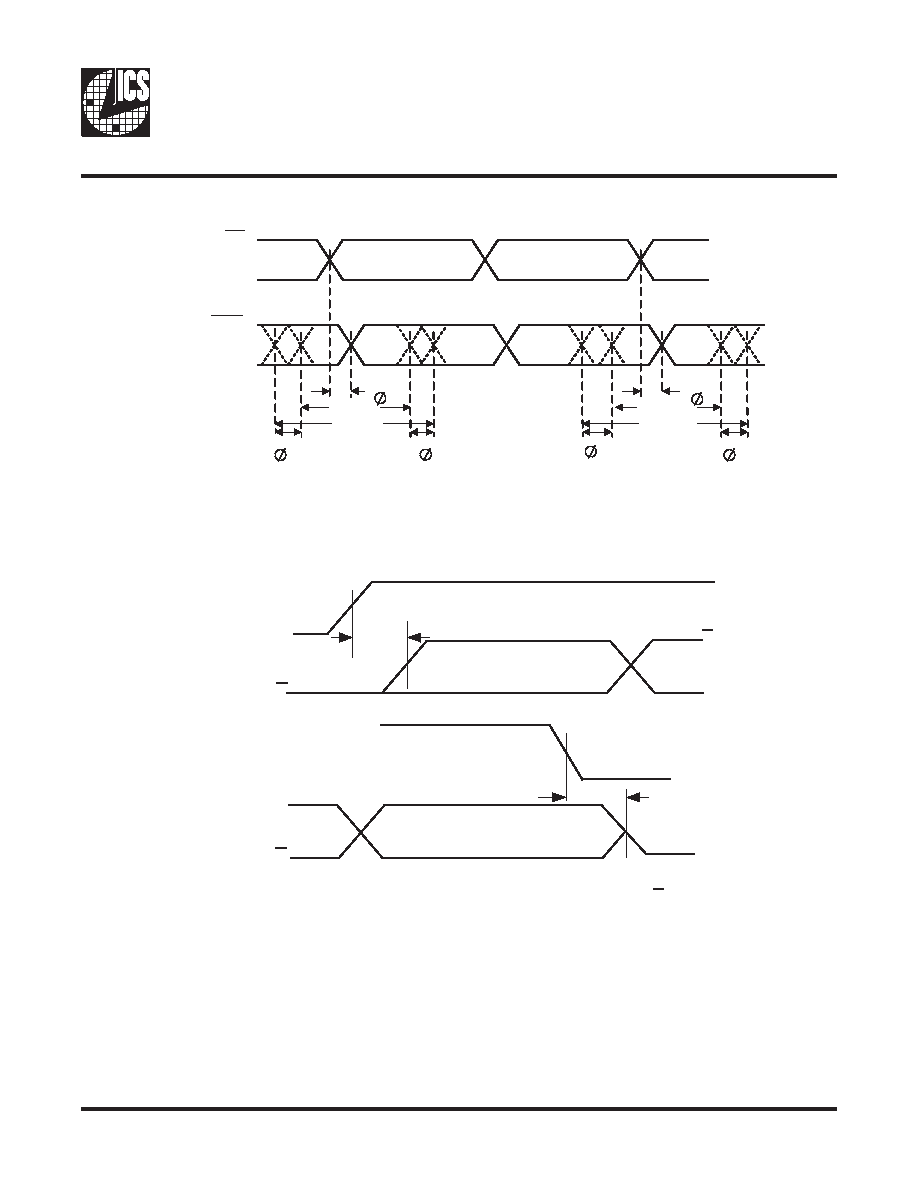

Figure 9. Dynamic Phase Offset

Figure 10. Time delay between OE and Clock Output (Y, Y)

t

( )

t

( )

FBIN

CK

t

( )dyn

t

( )dyn

t

( )dyn

t

( )dyn

SSC OFF

SSC ON

SSC OFF

50% VDDQ

ten

tdis

OE

Y/ Y

Y

50% VDDQ

Y

50% VDDQ

50 % VDDQ

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 97ULP877BHLF | 97ULP SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA52 |

| 97ULP877BKLF | 97ULP SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQCC40 |

| 97ULP877BH | 97ULP SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA52 |

| 97ULPA877AHLF-T | 97ULP SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA52 |

| 980-1 | 0 MHz - 3000 MHz, 140 deg - RF/MICROWAVE COAXIAL MECHANICAL PH SHIFTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 97ULP877BKLF/W | 制造商:Integrated Device Technology Inc 功能描述:ZERO DLY PLL CLOCK DRVR SGL 95MHZ TO 410MHZ 40PIN VFQFPN - Tape and Reel |

| 97ULP878AH | 制造商:Integrated Device Technology Inc 功能描述:97ULP878AH - Trays |

| 97ULP878AHLF | 制造商:Integrated Device Technology Inc 功能描述:97ULP878AHLF - Trays |

| 97ULP878AHLFT | 制造商:Integrated Device Technology Inc 功能描述:97ULP878AHLFT - Tape and Reel |

| 97ULP878AHT | 制造商:Integrated Device Technology Inc 功能描述:97ULP878AHT - Tape and Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。