- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382826 > 79RC32438 (Integrated Device Technology, Inc.) IDTTM InterpriseTM Integrated Communications Processor PDF資料下載

參數(shù)資料

| 型號: | 79RC32438 |

| 廠商: | Integrated Device Technology, Inc. |

| 英文描述: | IDTTM InterpriseTM Integrated Communications Processor |

| 中文描述: | IDTTM InterpriseTM集成通信處理器 |

| 文件頁數(shù): | 15/59頁 |

| 文件大小: | 644K |

| 代理商: | 79RC32438 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁

15 of 59

May 25, 2004

IDT 79RC32438

Boot Configuration Vector

The boot configuration vector is read by the RC32438 during a cold reset. The vector defines essential RC32438 parameters that are required

once the cold reset completes.

The encoding of the boot configuration vector is described in Table 3, and the vector input is illustrated in Figure 4. The value of the boot configura-

tion vector read in by the RC32438 during a cold reset may be determined by reading the Boot Configuration Vector (BCV) Register.

Miscellaneous

CLK

I

LVTTL

STI

EXTCLK

O

LVTTL

High Drive

COLDRSTN

I

LVTTL

STI

RSTN

I/O

LVTTL

Low Drive / STI

pull-up

pull-up on board

1.

External pull-up required in most system applications. Some applications may require additional pull-ups not identified in this table.

2.

Schmidt Trigger Input (STI).

3.

The PCI pins have internal pull-ups but they are too weak to guarantee system validity. Therefore, board pull-ups are mandatory

where indicated. GPIO alternate function pins for PCI must also have board pull-ups.

4.

PCIMUINTN is an alternate function of GPIO[30]. When configured as an alternate function, this pin is tri-stated when not asserted

(i.e., it acts as an open collector output).

5.

Use a 2.2K pull-up resistor for I2C pins.

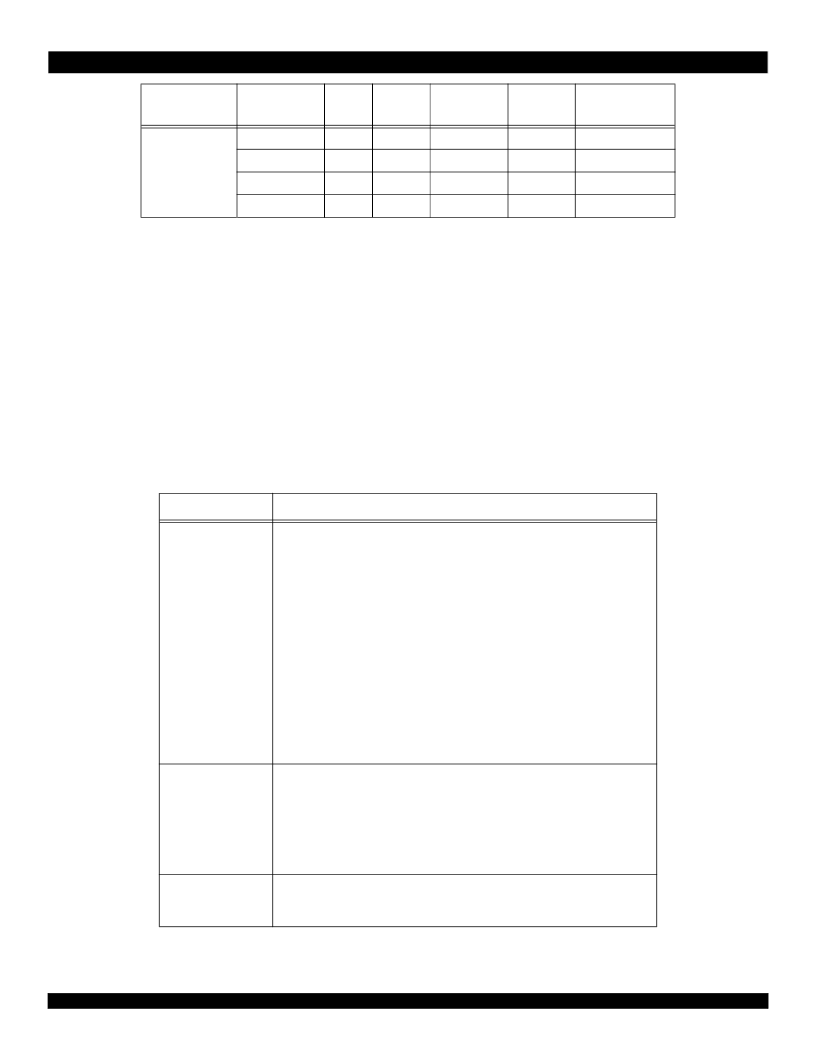

Signal

Name/Description

MDATA[3:0]

CPU Pipeline Clock Multiplier

. This field specifies the value by which the PLL multi-

plies the master clock input (CLK) to obtain the processor clock frequency (PCLK). For

master clock input frequency constraints, refer to Table 3.1 in the RC32438 User Man-

ual.

0x0 - PLL Bypass

0x1 - Multiply by 3

0x2 - Multiply by 4

0x3 - Multiply by 6

0x4 - Multiply by 8

0x5 - reserved

0x6 - reserved

0x7 - reserved

0x8 - reserved

0xD - reserved

0xE - reserved

0xF - reserved

MDATA[5:4]

External Clock Divider

. This field specifies the value by which the IPBus clock

(ICLK), which is always 1/2 PCLK, is divided in order to generate the external clock

output on the EXTCLK pin.

0x0 - Divide by 1

0x1 - Divide by 2

0x2 - Divide by 4

0x3 - reserved

MDATA[6]

Endian.

This bit specifies the endianness.

0x0 - little endian

0x1 - big endian

Table 3 Boot Configuration Encoding (Part 1 of 2)

Function

Pin Name

Type

Buffer

I/O Type

Internal

Resistor

Notes

1

Table 2 Pin Characteristics (Part 4 of 4)

相關PDF資料 |

PDF描述 |

|---|---|

| 79RC32K438-200BB | IDTTM InterpriseTM Integrated Communications Processor |

| 79RC32K438-200BBI | IDTTM InterpriseTM Integrated Communications Processor |

| 79RC32K438-233BB | IDTTM InterpriseTM Integrated Communications Processor |

| 79RC32K438-233BBI | IDTTM InterpriseTM Integrated Communications Processor |

| 79RC32K438-266BB | IDTTM InterpriseTM Integrated Communications Processor |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 79RC32438-200BB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| 79RC32438-200BBI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| 79RC32438-233BB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| 79RC32438-233BBI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| 79RC32H434-266BC | 功能描述:處理器 - 專門應用 RoHS:否 制造商:Freescale Semiconductor 類型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

發(fā)布緊急采購,3分鐘左右您將得到回復。