- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382826 > 79RC32355133DHI (Integrated Device Technology, Inc.) Communications Processor PDF資料下載

參數(shù)資料

| 型號(hào): | 79RC32355133DHI |

| 廠商: | Integrated Device Technology, Inc. |

| 英文描述: | Communications Processor |

| 中文描述: | 通信處理器 |

| 文件頁數(shù): | 18/47頁 |

| 文件大小: | 987K |

| 代理商: | 79RC32355133DHI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當(dāng)前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁

18 of 47

May 25, 2004

IDT 79RC32355

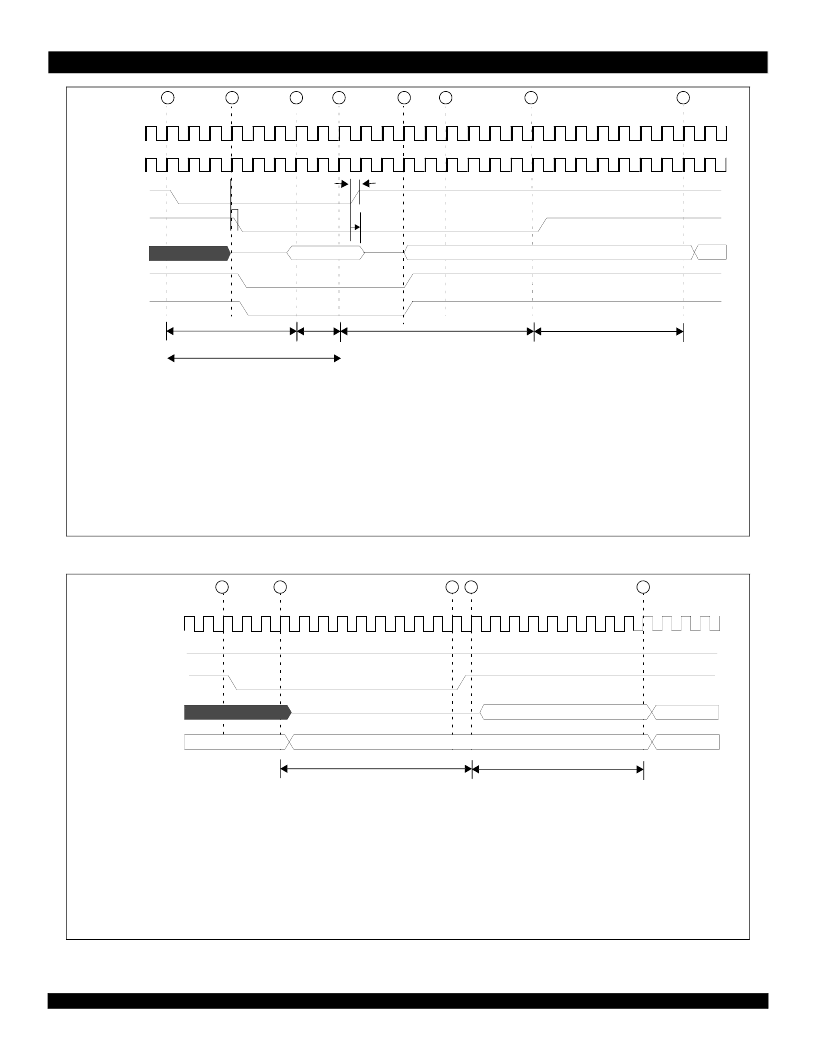

Figure 6 Cold Reset AC Timing Waveform

Figure 7 Warm Reset AC Timing Waveform

BOOT VECT

SYSCLKP

COLDRSTN

RSTN

MDATA[31:0]

BDIRN

BOEN[0]

>= 100 ms

>=10ms

>= 4096 CLKP clock cycles

OR

>= 64 CLKP clock cycles

*

>= 4096 CLKP clock cycles

OR

>= 64 CLKP clock cycles

*

*

Selection of 4096 or 64 cycles is selected by the boot configuration vector (fast reset).

Tpw1

Tdo2

CLKP

1

FFFF_FFFF

Thld3

1.

COLDRSTN asserted by external logic.

2.

The RC32355 asserts RSTN, asserts BOEN[0] low, drives BDIRN low, and tri-states the data bus in response.

3.

External logic begins driving valid boot configuration vector on the data bus, and the RC32355 starts sampling it.

4.

External logic negates COLDRSTN and tri-states the boot configuration vector on MDATA[15:0]. The boot configuration vector must not be tri-stated before COLDRSTN is deas-

serted. The RC32355 stops sampling the boot configuration vector.

5.

The RC32355 starts driving the data bus, MDATA[31:0], deasserts BOEN[0] high, and drives BDIRN high.

6.

SYSCLKP may be held constant after this point if Hold SYSCLKP Constant is selected in the boot configuration vector.

7.

RSTN negated by RC32355.

8.

CPU begins executing by taking MIPS reset exception, and the RC32355 starts sampling RSTN as a warm reset input.

2

3

4

5

6

7

8

Trise1

Active

Deasserted

Active

CLKP

COLDRSTN

RSTN

MDATA[31:0]

Mem Control Signals

>= 4096 CLKP clock cycles

OR

>= 64 CLKP clock cycles

*

>= 4096 CLKP clock cycles

OR

>= 64 CLKP clock cycles

*

(RSTN ignored during this period

to allow pull-up to drive signal high)

*

Selection of 4096 or 64 cycles is selected by the boot configuration vector (fast reset).

1.

Warm reset condition caused by either RSTN asserted, write to reset register, or bus transaction timer time-out. The RC32355 asserts RSTN output low in response.

2.

The RC32355 tri-states the data bus, MDATA[31:0], and deasserts all memory control signals, such as RASN, CASN, RWN, OEN, etc.

3.

The RC32355 deasserts RSTN.

4.

The RC32355 starts driving the data bus, MDATA[31:0], again, but does not sample the RSTN input.

5.

CPU begins executing by taking a MIPS soft reset exception and also starts sampling the RSTN input again.

FFFF_FFFF

1

2

3

4

5

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 79RC32364 | RISController Embedded 32-bit Microprocessor, based on RISCore32300 |

| 79RC32V364100DA | RISController Embedded 32-bit Microprocessor, based on RISCore32300 |

| 79RC32V364100DAI | RISController Embedded 32-bit Microprocessor, based on RISCore32300 |

| 79RC32V364133DA | RISController Embedded 32-bit Microprocessor, based on RISCore32300 |

| 79RC32V364133DAI | RISController Embedded 32-bit Microprocessor, based on RISCore32300 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 79RC32355-133DHI | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:IDT Interprise Integrated Communications Processor |

| 79RC32355150DH | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:Communications Processor |

| 79RC32355-150DH | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:IDT Interprise Integrated Communications Processor |

| 79RC32355150DHI | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:Communications Processor |

| 79RC32355-150DHI | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:IDT Interprise Integrated Communications Processor |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。