- 您現在的位置:買賣IC網 > PDF目錄382826 > 79RC32355133DHI (Integrated Device Technology, Inc.) Communications Processor PDF資料下載

參數資料

| 型號: | 79RC32355133DHI |

| 廠商: | Integrated Device Technology, Inc. |

| 英文描述: | Communications Processor |

| 中文描述: | 通信處理器 |

| 文件頁數: | 10/47頁 |

| 文件大小: | 987K |

| 代理商: | 79RC32355133DHI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁

10 of 47

May 25, 2004

IDT 79RC32355

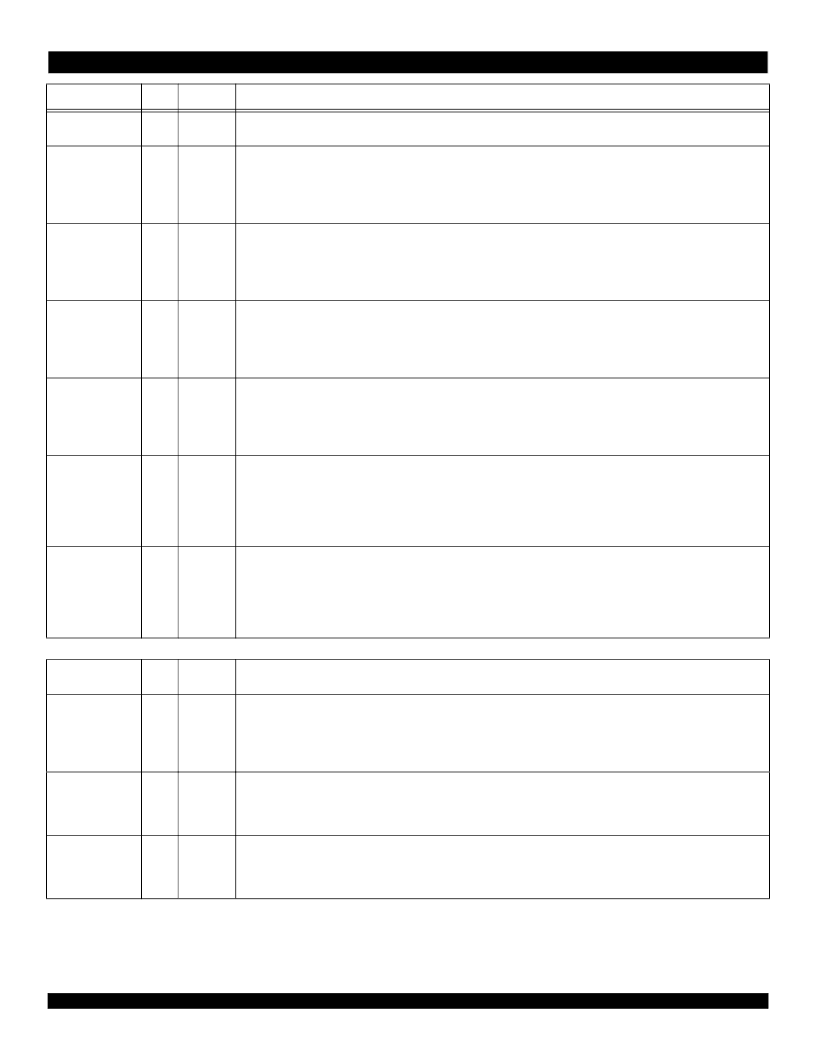

JTAG_TMS

I

STI

JTAG Mode Select

. This input signal is decoded by the tap controller to control test operation. This signal requires an

external resistor, listed in Table 16.

EJTAG_PCST[0]

O

Low Drive

PC trace status.

This bus gives the PC trace status information during EJTAG/ICE mode. EJTAG/ICE enable is selected

during reset using the boot configuration and overrides the selection of the Primary and Alternate functions. This signal

requires an external resistor, listed in Table 16.

Primary function: General Purpose I/O, GPIOP[10].

1st Alternate function: UART channel 1 data terminal ready, U1DTRN.

EJTAG_PCST[1]

O

Low Drive

PC trace status.

This bus gives the PC trace status information during EJTAG/ICE mode. EJTAG/ICE enable is selected

during reset using the boot configuration and overrides the selection of the Primary and Alternate functions. This signal

requires an external resistor, listed in Table 16.

Primary function: General Purpose I/O, GPIOP[11]. At reset, this pin defaults to primary function GPIOP[11].

1st Alternate function: UART channel 1 data set ready, U1DSRN.

EJTAG_PCST[2]

O

Low Drive

PC trace status.

This bus gives the PC trace status information during EJTAG/ICE mode. EJTAG/ICE enable is selected

during reset using the boot configuration and overrides the selection of the Primary and Alternate functions. This signal

requires an external resistor, listed in Table 16.

Primary function: General Purpose I/O, GPIOP[12].

1st Alternate function: UART channel 1 request to send, U1RTSN.

EJTAG_DCLK

O

Low Drive

PC trace clock.

This is used to capture address and data during EJTAG/ICE mode. EJTAG/ICE enable is selected during

reset using the boot configuration and overrides the selection of the Primary and Alternate functions. This signal requires

an external resistor, listed in Table 16.

Primary function: General Purpose I/O, GPIOP[13].

1st Alternate function: UART channel 1 clear to send, U1CTSN.

EJTAG_TRST_N

I

STI

EJTAG Test Reset.

EJTAG_TRST_N is an active-low signal for asynchronous reset of only the EJTAG/ICE controller.

EJTAG_TRST_N requires an external pull-up on the board. EJTAG/ICE enable is selected during reset using the boot con-

figuration and overrides the selection of the Primary and Alternate functions. This signal requires an external resistor, listed

in Table 16.

Primary: General Purpose I/O, GPIOP[31]

1st Alternate function: DMA finished output, DMAFIN.

JTAG_TRST_N

I

STI

JTAG Test Reset.

JTAG_TRST_N is an active-low signal for asynchronous reset of only the JTAG boundary scan control-

ler. JTAG_TRST_N requires an external pull-down on the board that will hold the JTAG boundary scan controller in reset

when not in use if selected. JTAG reset enable is selected during reset using the boot configuration and overrides the

selection of the Primary and Alternate functions.

Primary function: General Purpose I/O, GPIOP[2].

1st Alternate function: UART channel 0 ring indicator, U0RIN.

Debug

INSTP

O

Low Drive

Instruction or Data Indicator

. This signal is driven high during CPU instruction fetches and low during CPU data transac-

tions on the memory and peripheral bus.

CPUP

O

Low Drive

CPU or DMA Transaction Indicator

. This signal is driven high during CPU transactions and low during DMA transactions

on the memory and peripheral bus if CPU/DMA Transaction Indicator Enable is enabled. CPU/DMA Status mode enable is

selected during reset using the boot configuration and overrides the selection of the Primary and Alternate functions.

Primary function: General Purpose I/O, GPIOP[4].

1st Alternate function: UART channel 0 data terminal ready U0DTRN.

DMAP[0]

O

Low Drive

Active DMA channel code

. DMA debug enable is selected during reset using the boot configuration and overrides the

selection of the Primary and Alternate functions.

Primary function: General Purpose I/O, GPIOP[23].

1st Alternate function: TXADDR[1].

DMAP[1]

O

Low Drive

Active DMA channel code

. DMA debug enable is selected during reset using the boot configuration and overrides the

selection of the Primary and Alternate functions.

Primary function: General Purpose I/O, GPIOP[25].

1st Alternate function: RXADDR[1].

Name

Type I/O Type

Description

Table 1 Pin Descriptions (Part 6 of 8)

相關PDF資料 |

PDF描述 |

|---|---|

| 79RC32364 | RISController Embedded 32-bit Microprocessor, based on RISCore32300 |

| 79RC32V364100DA | RISController Embedded 32-bit Microprocessor, based on RISCore32300 |

| 79RC32V364100DAI | RISController Embedded 32-bit Microprocessor, based on RISCore32300 |

| 79RC32V364133DA | RISController Embedded 32-bit Microprocessor, based on RISCore32300 |

| 79RC32V364133DAI | RISController Embedded 32-bit Microprocessor, based on RISCore32300 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| 79RC32355-133DHI | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:IDT Interprise Integrated Communications Processor |

| 79RC32355150DH | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:Communications Processor |

| 79RC32355-150DH | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:IDT Interprise Integrated Communications Processor |

| 79RC32355150DHI | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:Communications Processor |

| 79RC32355-150DHI | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:IDT Interprise Integrated Communications Processor |

發(fā)布緊急采購,3分鐘左右您將得到回復。