- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄158051 > 71V3557SA85BG8 (INTEGRATED DEVICE TECHNOLOGY INC) 128K X 36 ZBT SRAM, 8.5 ns, PBGA119 PDF資料下載

參數(shù)資料

| 型號(hào): | 71V3557SA85BG8 |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | SRAM |

| 英文描述: | 128K X 36 ZBT SRAM, 8.5 ns, PBGA119 |

| 封裝: | 14 X 22 MM, POWER, PLASTIC, BGA-119 |

| 文件頁數(shù): | 8/28頁 |

| 文件大?。?/td> | 511K |

| 代理商: | 71V3557SA85BG8 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當(dāng)前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

6.42

16

IDT71V3557, IDT71V3559, 128K x 36, 256K x 18, 3.3V Synchronous SRAMs with

ZBT Feature, 3.3V I/O, Burst Counter, and Flow-Through Outputs

Commercial and Industrial Temperature Ranges

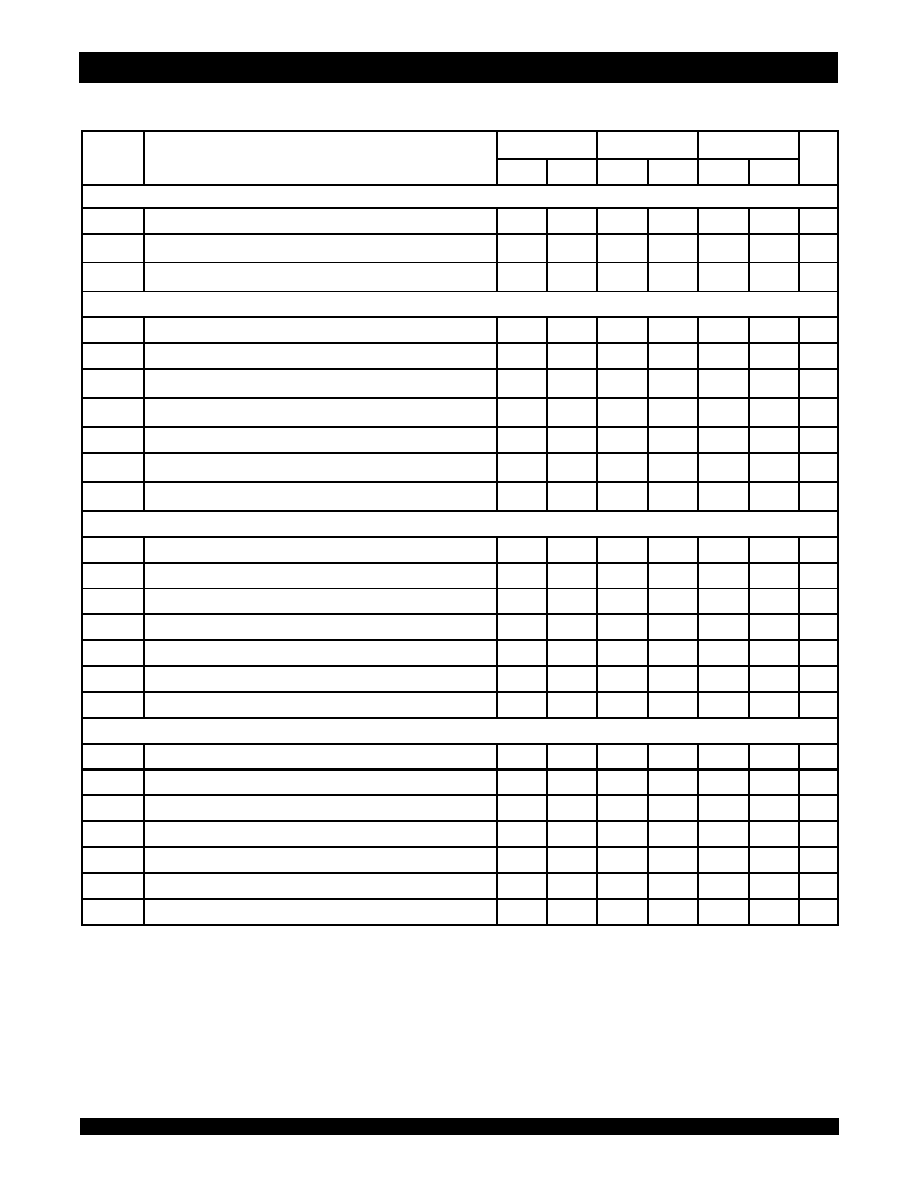

AC Electrical Characteristics

(VDD = 3.3V +/-5%, Commercial and Industrial Temperature Ranges)

NOTES:

1. Measured as HIGH above 0.6VDDQ and LOW below 0.4VDDQ.

2. Transition is measured ±200mV from steady-state.

3. These parameters are guaranteed with the AC load (Figure 1) by device characterization. They are not production tested.

4. To avoid bus contention, the output buffers are designed such that tCHZ (device turn-off) is about 1ns faster than tCLZ (device turn-on) at a given temperature and

voltage. The specs as shown do not imply bus contention because tCLZ is a Min. parameter that is worse case at totally different test conditions

(0 deg. C, 3.465V) than tCHZ, which is a Max. parameter (worse case at 70 deg. C, 3.135V).

5. Commercial temperature range only.

7.5ns(5)

8ns

8.5ns

Symbol

Parameter

Min.

Max.

Min.

Max.

Min.

Max.

Unit

tCYC

Clock Cycle Time

10

____

10.5

____

11

____

ns

tCH(1)

Clock High Pulse Width

2.5

____

2.7

____

3.0

____

ns

tCL(1)

Clock Low Pulse Width

2.5

____

2.7

____

3.0

____

ns

Output Parameters

tCD

Clock High to Valid Data

____

7.5

____

8

____

8.5

ns

tCDC

Clock High to Data Change

2

____

2

____

2

____

ns

tCLZ(2,3,4)

Clock High to Output Active

3

____

3

____

3

____

ns

tCHZ(2,3,4)

Clock High to Data High-Z

____

5

____

5

____

5ns

tOE

Output Enable Access Time

____

5

____

5

____

5ns

tOLZ(2,3)

Output Enable Low to Data Active

0

____

0

____

0

____

ns

tOHZ(2,3)

Output Enable High to Data High-Z

____

5

____

5

____

5ns

Set Up Times

tSE

Clock Enable Setup Time

2.0

____

2.0

____

2.0

____

ns

tSA

Address Setup Time

2.0

____

2.0

____

2.0

____

ns

tSD

Data In Setup Time

2.0

____

2.0

____

2.0

____

ns

tSW

Read/Write (R/

W) Setup Time

2.0

____

2.0

____

2.0

____

ns

tSADV

Advance/Load (ADV/

LD) Setup Time

2.0

____

2.0

____

2.0

____

ns

tSC

Chip Enable/Select Setup Time

2.0

____

2.0

____

2.0

____

ns

tSB

Byte Write Enable (

BWx) Setup Time

2.0

____

2.0

____

2.0

____

ns

Hold Times

tHE

Clock Enable Hold Time

0.5

____

0.5

____

0.5

____

ns

tHA

Address Hold Time

0.5

____

0.5

____

0.5

____

ns

tHD

Data In Hold Time

0.5

____

0.5

____

0.5

____

ns

tHW

Read/Write (R/

W) Hold Time

0.5

____

0.5

____

0.5

____

ns

tHADV

Advance/Load (ADV/

LD) Hold Time

0.5

____

0.5

____

0.5

____

ns

tHC

Chip Enable/Select Hold Time

0.5

____

0.5

____

0.5

____

ns

tHB

Byte Write Enable (

BWx) Hold Time

0.5

____

0.5

____

0.5

____

ns

5282 tbl 24

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 71V67703S75BQ | 256K X 36 CACHE SRAM, 7.5 ns, PBGA165 |

| 72-30-33 | 0 MHz - 4000 MHz RF/MICROWAVE FIXED ATTENUATOR |

| 72-40-43 | 0 MHz - 4000 MHz RF/MICROWAVE FIXED ATTENUATOR |

| 72-10-14 | 0 MHz - 4000 MHz RF/MICROWAVE FIXED ATTENUATOR |

| 72-30-13 | 0 MHz - 4000 MHz RF/MICROWAVE FIXED ATTENUATOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 71V3558S100PFG | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| 71V3558S100PFG8 | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| 71V3558S100PFGI | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| 71V3558S100PFGI8 | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| 71V3558S133BG | 制造商:Integrated Device Technology Inc 功能描述:4.5MBIT SRAM CHIP SYNC SINGLE 3.3V 256K X 18 4.2NS - Trays 制造商:Integrated Device Technology Inc 功能描述:IDT 71V3558S133BG, 4.5MBit SRAM Chip Sync Single 3.3V 256K x 18 4.2ns 119-Pin BGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。