- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄68811 > 71M6543F-IGT/F (MAXIM INTEGRATED PRODUCTS INC) SPECIALTY ANALOG CIRCUIT, PQFP100 PDF資料下載

參數(shù)資料

| 型號(hào): | 71M6543F-IGT/F |

| 廠(chǎng)商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分類(lèi): | 模擬信號(hào)調(diào)理 |

| 英文描述: | SPECIALTY ANALOG CIRCUIT, PQFP100 |

| 封裝: | LEAD FREE, LQFP-100 |

| 文件頁(yè)數(shù): | 29/157頁(yè) |

| 文件大?。?/td> | 2178K |

| 代理商: | 71M6543F-IGT/F |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)當(dāng)前第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)

71M6543F/H and 71M6543G/GH Data Sheet

124

2008–2011 Teridian Semiconductor Corporation

v1.2

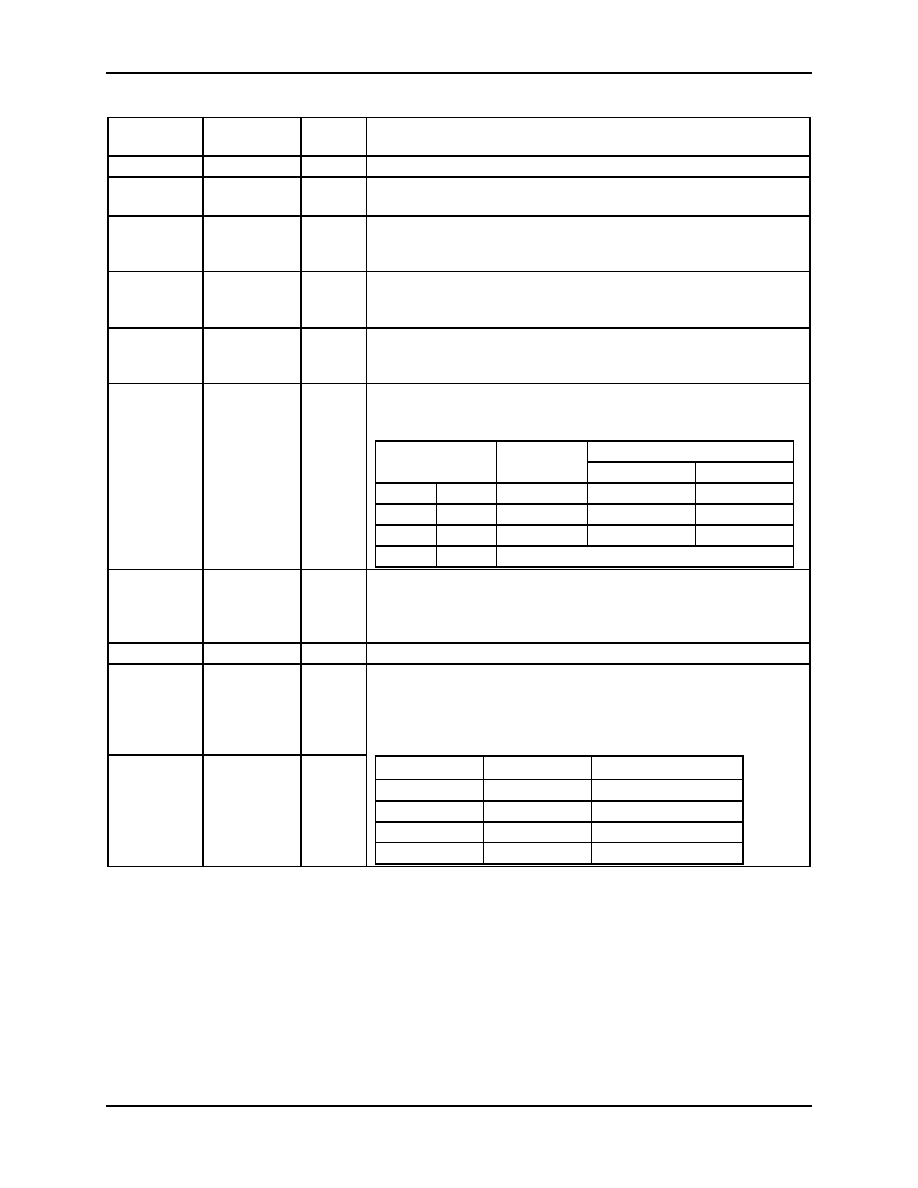

Table 78: CECONFIG Bit Definitions (CE RAM 0x20)

CECONFIG

bit

Name

Default

Description

23

Reserved

0

Reserved.

22

EXT_TEMP

0

When 1, the MPU controls temperature compensation via the

GAIN_ADJn (CE RAM 0x40-0x42), when 0, the CE is in control.

21

EDGE_INT

1

When 1, XPULSE produces a pulse for each zero-crossing of

the mains phase selected by FREQSEL[1:0] , which can be used

to interrupt the MPU.

20

SAG_INT

1

When 1, activates the YPULSE/SEGDIO7 output when a sag is

detected (see 2.5.10) on the phase selected with FREQ-

SEL[1:0].

19:8

SAG_CNT

218

(0xDA)

The number of consecutive voltage samples below SAG_THR

(CE RAM 0x24) before a sag alarm is declared. The default value

is equivalent to 100 ms.

7:6

FREQSEL[1:0]

0

FREQSEL[1:0] selects the phase to be used for the frequency

monitor, sag detection, the phase-to-phase lag calculation and

for the zero crossing counter (MAINEDGE_X, CE RAM 0x83).

FREQ SEL[1:0]

Phase

Selected

Phases Selected

PH_AtoB_X

PH_AtoC_X

0

A

A-B

A-C

0

1

B

B-C

B-A

1

0

C

C-A

C-B

1

Not allowed

5

EXT_PULSE

1

When zero, causes the pulse generators to respond to internal

data. WPULSE = WSUM_X (CE RAM 0x84), VPULSE = VARSUM_X

(CE RAM 0x88.) Otherwise, the generators respond to values the

MPU places in APULSEW and APULSER (CE RAM 0x45 and 0x49)

4:2

Reserved

0

Reserved.

1

PULSE_FAST

0

When PULSE_FAST = 1, the pulse generator input is increased

16x. When PULSE_SLOW = 1, the pulse generator input is

reduced by a factor of 64. These two parameters control the

pulse gain factor X (see table below). Allowed values are either

1 or 0. Default is 0 for both (X = 6).

PULSE_FAST PULSE_SLOW

X

0

1.5 * 2

2 = 6

0

1

1.5 * 2

-4 = 0.09375

1

0

1.5 * 2

6 = 96

1

Do not use

0

PULSE_SLOW

0

The FREQSEL[1:0] field in CECONFIG (CE RAM 0x20[7:6]) selects the phase that is utilized to generate a sag

interrupt. Thus, a SAG_INT event occurs when the selected phase has satisfied the sag event criteria as

set by the SAG_THR (CE RAM 0x24) register and the SAG_CNT field in CECONFIG (CE RAM 0x20[19:8]).

When the SAG_INT bit (CE RAM 0x20[20]) is set to 1, a sag event generates a transition on the YPULSE

output. After a sag interrupt, the MPU should change the FREQSEL[1:0] setting to select the other phase,

if it is powered. Even though a sag interrupt is only generated on the selected phase, all three phases

are simultaneously checked for sag. The presence of power on a given phase can be sensed by directly

checking the SAG_A, SAG_B and SAG_C bits in CESTATUS (CE RAM 0x80[0:1]).

The EXT_TEMP bit enables temperature compensation by the MPU, when set to 1. When 0, internal (CE)

temperature compensation is enabled.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 71M6543H-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP100 |

| 71M6543F-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP100 |

| 71M6543H-IGT/F | SPECIALTY ANALOG CIRCUIT, PQFP100 |

| 71M6543G-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP100 |

| 71M6543GH-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP100 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 71M6543F-IGTR/F | 功能描述:計(jì)量片上系統(tǒng) - SoC Precision Energy Meter IC RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 處理器系列:71M6511 類(lèi)型:Metering SoC 最大時(shí)鐘頻率:70 Hz 程序存儲(chǔ)器大小:64 KB 數(shù)據(jù) RAM 大小:7 KB 接口類(lèi)型:UART 可編程輸入/輸出端數(shù)量:12 片上 ADC: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:LQFP-64 封裝:Reel |

| 71M6543FT-IGT/F | 制造商:Maxim Integrated Products 功能描述:ENERGY METER ICS - Rail/Tube |

| 71M6543FT-IGTR/F | 制造商:Maxim Integrated Products 功能描述:3-PHASE SOC, 64KB FLASH, PRES TEMP SENSOR - Tape and Reel |

| 71M6543G | 制造商:MAXIM 制造商全稱(chēng):Maxim Integrated Products 功能描述:Selectable Gain of 1 or 8 for One Current Energy Meter ICs Metrology Compensation |

| 71M6543GH | 制造商:未知廠(chǎng)家 制造商全稱(chēng):未知廠(chǎng)家 功能描述:電表IC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。