- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄68811 > 71M6532F-IGTR/F (MAXIM INTEGRATED PRODUCTS INC) 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PQFP100 PDF資料下載

參數(shù)資料

| 型號(hào): | 71M6532F-IGTR/F |

| 廠商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分類: | 電源管理 |

| 英文描述: | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PQFP100 |

| 封裝: | LEAD FREE, LQFP-100 |

| 文件頁(yè)數(shù): | 34/120頁(yè) |

| 文件大小: | 2477K |

| 代理商: | 71M6532F-IGTR/F |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)當(dāng)前第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)

Data Sheet 71M6531D/F-71M6532D/F

FDS 6531/6532 005

20

2005-2010 TERIDIAN Semiconductor Corporation

v1.3

The 80515 writes into external data memory when the MPU executes a MOVX @Ri,A or MOVX

@DPTR,A instruction. The MPU reads external data memory by executing a MOVX A,@Ri or MOVX

A,@DPTR instruction (SFR PDATA provides the upper 8 bytes for the MOVX A,@Ri instruction).

Internal and External Memory Map

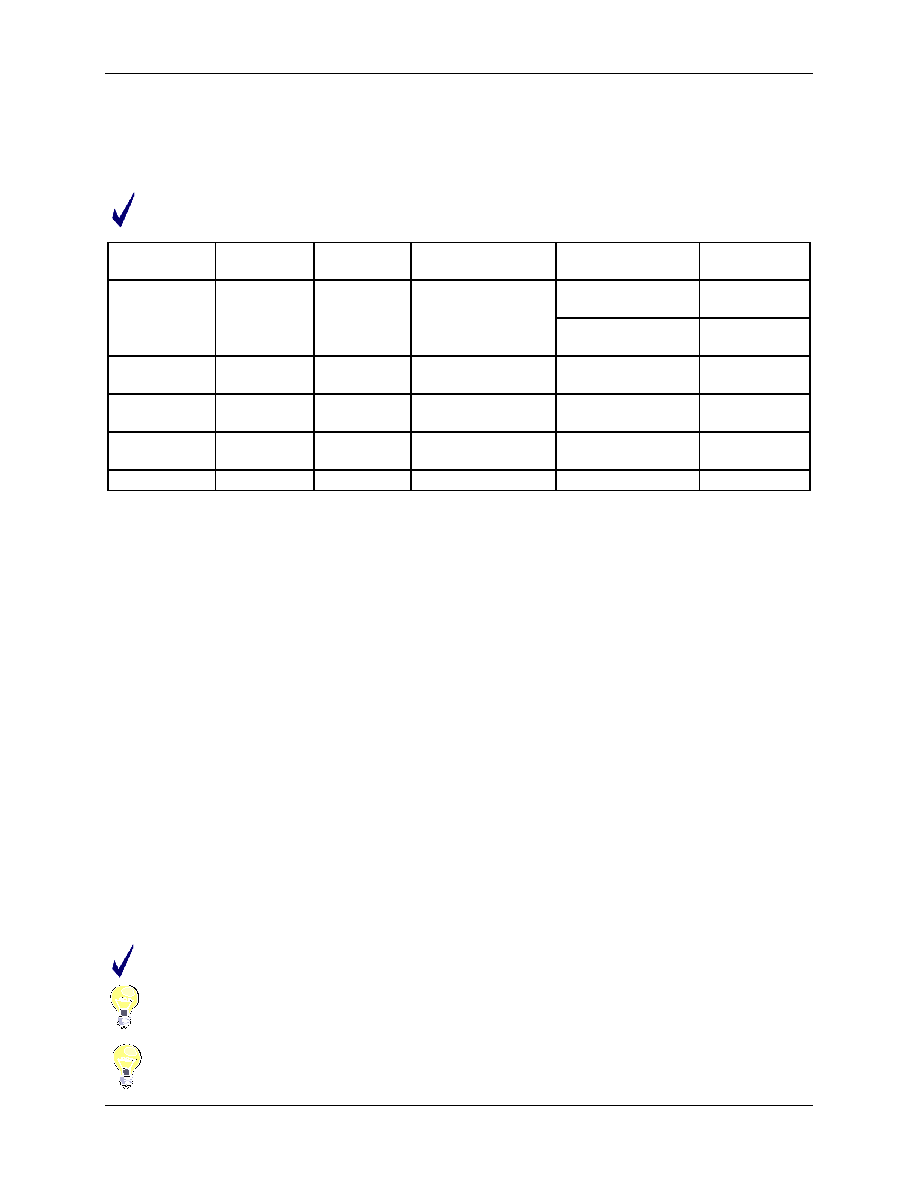

Table 7 shows the address, type, use and size of the various memory components.

Only the memory ranges shown in Table 7 contain physical memory.

Table 7: Memory Map

Address

(hex)

Memory

Technology

Memory

Type

Name

Typical Usage

Memory Size

(bytes)

00000-1FFFF/

00000-3FFFF

Flash

Memory

Non-volatile

Program memory

for MPU and CE

MPU Program and

non-volatile data

128 KB/

256 KB

CE program (on 1

KB boundary)

8 KB max.

0000-0FFF

Static RAM

Volatile

External RAM

(XRAM)

Shared by CE and

MPU

4 KB

2000-20BF,

20C8-20FF

Static RAM

Volatile

Configuration RAM,

I/O RAM

Hardware control

256

20C0-20C7

Static RAM

Non-volatile

(battery)

Configuration RAM,

I/O RAM

Battery-buffered

memory

8

0000-00FF

Static RAM

Volatile

Internal RAM

Part of 80515 Core

256

Memory size depends on the IC. See Section1.5.5 Physical Memory for details.

MOVX Addressing

There are two types of instructions differing in whether they provide an 8-bit or 16-bit indirect address to

the external data RAM.

In the first type, MOVX A,@Ri, the contents of R0 or R1 in the current register bank provide the eight

lower-ordered bits of address. The eight high-ordered bits of the address are specified with the PDATA

SFR. This method allows the user paged access (256 pages of 256 bytes each) to all ranges of the

external data RAM.

In the second type of MOVX instruction, MOVX A,@DPTR, the data pointer generates a 16-bit address.

This form is faster and more efficient when accessing very large data arrays (up to 64 KB), since no

additional instructions are needed to set up the eight high ordered bits of the address.

It is possible to mix the two MOVX types. This provides the user with four separate data pointers, two

with direct access and two with paged access, to the entire 64 KB of external memory range.

Dual Data Pointer

The Dual Data Pointer accelerates the block moves of data. The standard DPTR is a 16-bit register that

is used to address external memory or peripherals. In the 80515 core, the standard data pointer is called

DPTR, the second data pointer is called DPTR1. The data pointer select bit, located in the LSB of the DPS

register (DPS[0]), chooses the active pointer. DPTR is selected when DPS[0] = 0 and DPTR1 is selected

when DPS[0] = 1.

The user switches between pointers by toggling the LSB of the DPS register. The values in the data pointers

are not affected by the LSB of the DPS register. All DPTR related instructions use the currently selected

DPTR for any activity.

The second data pointer may not be supported by certain compilers.

DPTR1 is useful for copy routines, where it can make the inner loop of the routine two instructions faster

compared to the reloading of DPTR from registers. Any interrupt routine using DPTR1 must save

and restore DPS, DPTR and DPTR1, which increases stack usage and slows down interrupt latency.

By selecting the Evatronics R80515 core in the Keil compiler project settings and by using the

compiler directive “MODC2”, dual data pointers are enabled in certain library routines.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 71M6534-IGT/F | SPECIALTY ANALOG CIRCUIT, PQFP120 |

| 71M6534H-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP120 |

| 71M6533H-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP100 |

| 71M6534-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP120 |

| 71M6534H-IGT/F | SPECIALTY ANALOG CIRCUIT, PQFP120 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 71M6533 | 制造商:TERIDIAN 制造商全稱:TERIDIAN 功能描述:Energy Meter IC |

| 71M6533-DB | 功能描述:開發(fā)板和工具包 - 8051 71M6533 Demo Brd RoHS:否 制造商:Silicon Labs 產(chǎn)品:Development Kits 工具用于評(píng)估:C8051F960, Si7005 核心: 接口類型:USB 工作電源電壓: |

| 71M6533G | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:Exceeds IEC 62053/ANSI C12.20 Standards |

| 71M6533G-IGTR/F | 功能描述:計(jì)量片上系統(tǒng) - SoC AC Power Monitoring SoC-Programd RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 處理器系列:71M6511 類型:Metering SoC 最大時(shí)鐘頻率:70 Hz 程序存儲(chǔ)器大小:64 KB 數(shù)據(jù) RAM 大小:7 KB 接口類型:UART 可編程輸入/輸出端數(shù)量:12 片上 ADC: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:LQFP-64 封裝:Reel |

| 71M6533H | 制造商:TERIDIAN 制造商全稱:TERIDIAN 功能描述:Energy Meter IC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。