- 您現在的位置:買賣IC網 > PDF目錄293977 > 5V80001PGGI (INTEGRATED DEVICE TECHNOLOGY INC) 98.304 MHz, OTHER CLOCK GENERATOR, PDSO20 PDF資料下載

參數資料

| 型號: | 5V80001PGGI |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | XO, clock |

| 英文描述: | 98.304 MHz, OTHER CLOCK GENERATOR, PDSO20 |

| 封裝: | 4.40 MM, ROHS COMPLIANT, TSSOP-20 |

| 文件頁數: | 9/15頁 |

| 文件大?。?/td> | 294K |

| 代理商: | 5V80001PGGI |

IDT5V80001

MOST CLOCK INTERFACE

SYNTHESIZERS

IDT MOST CLOCK INTERFACE

3

IDT5V80001

REV S 083109

Operation

The IDT5V80001 performs clock generation and recovery

for either a master or slave node in a MOST ring. It provides

a interface between a controller (typically implemented in an

ASIC or FPGA) and the fiber optic transceiver (FOT).

When used in a Master node (OEM = High), the Master PLL

synthesizes a frequency of twice the MOST data rate as the

MCLK output, and also reclocks the data from the controller

that is input on the FOT_IN pin to the INPUT_COPY output.

The output data on FOT_OUT is the MOST_Din data

retimed to MCLK if BYPASS is driven low, or the FOT_IN

data if BYPASS is driven high. Simultaneously, the device

recovers the clock from data on the FOT_IN pin and outputs

a 2x clock on RCLK.

In a slave node, OEM is set low and the MCLK output is

disabled. Data from the controller (FOT_IN) is retimed using

the recovered clock and output on the INPUT_COPY. If

BYPASS is driven high, the controller data (FOT_IN) is also

transmitted on the FOT_OUT output but is not retimed to

RCLK. If BYPASS is driven low, the MOST_Din data is

retimed and transmitted on the FOT_OUT output.

To recover the clock from the data stream, the two PLLs

work together. The lock sequence from power on is:

1. Crystal oscillator starts and stabilizes.

2. Master (frequency synthesis) PLL starts and locks to the

crystal.

3. CDR PLL starts and locks to the master PLL to obtain a

frequency operation point.

4. Activity is detected on FOT_IN.

5. CDR PLL phase-locks to incoming data.

Extreme conditions, such as electrical transients, phase

steps or brief dropouts on the FOT_IN pin may cause the

CDR PLL to unlock. If this occurs and the controller begins

to experience data errors, it should set RESET low for at

least 50 ns to restart the data lock sequence from step 3.

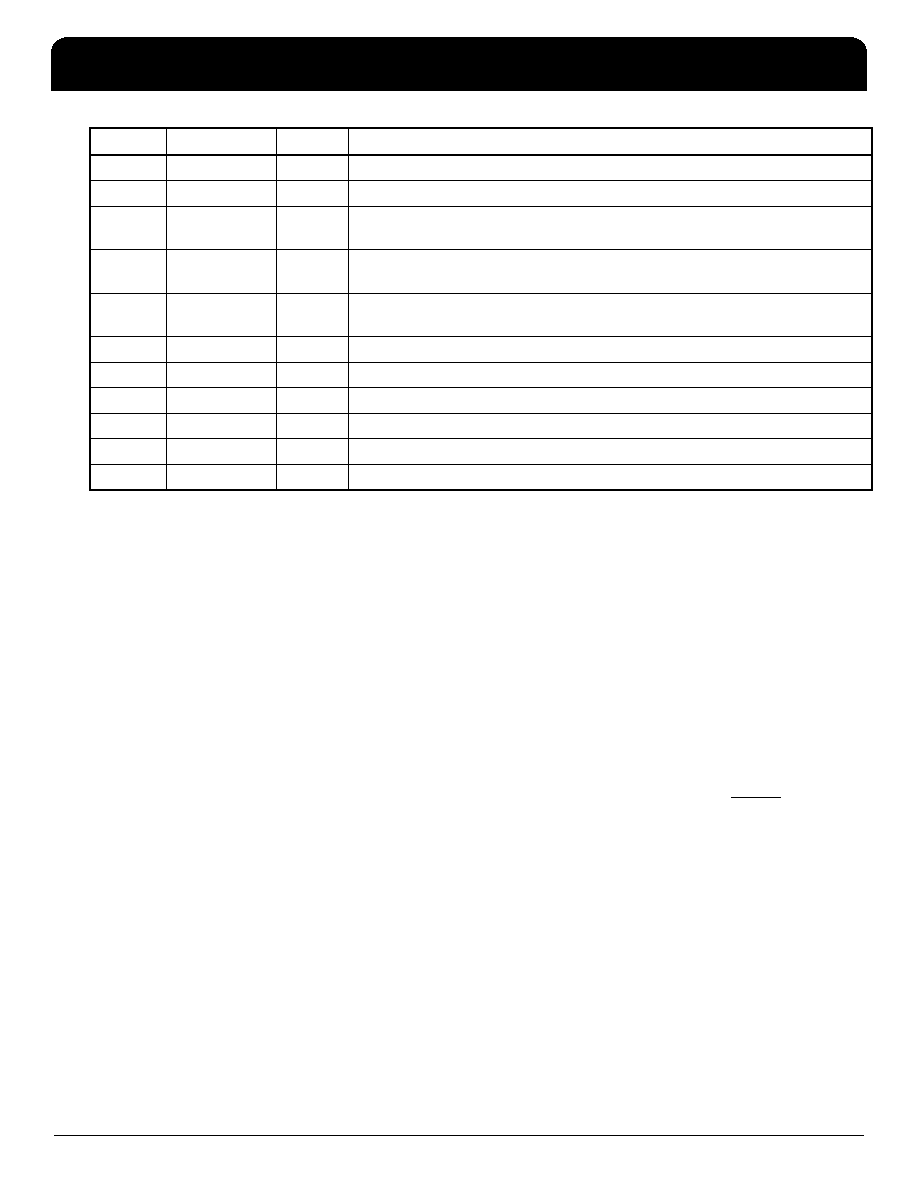

10

LF

Input

Loop filter connection for CDR PLL.

11

LFR

Input

Loop filter return. Connected to ground internally.

12

BYPASS

Input

MUX control to bypass CDR PLL. Active high. No internal pull-up or pull-down

resistor.

13

OEM

Input

High to enable MCLK. See table above. No internal pull-up or pull-down

resistor.

14

MCLK

Output

Master clock output. Clean clock derived from crystal. See table above. Weak

pull-down when OEM = 0.

15

GND

Power

Connect to ground.

16

RCLK

Output

Recovered clock out. See table above.

17

VDD

Power

Connect to 3.3 V supply.

18

INPUT_COPY

Output

Retimed copy of FOT_IN input.

19

MOST_Din

Input

MOST data input.

20

NC

—

No Connect. Do not connect this pin to anything.

Pin

Name

Type

Pin Description

相關PDF資料 |

PDF描述 |

|---|---|

| 6-1460821-1 | MALE-MALE, RF STRAIGHT ADAPTER, PLUG-PLUG |

| 6-1460821-2 | MALE-FEMALE, RF STRAIGHT ADAPTER, PLUG-JACK |

| 6-1460821-3 | MALE-FEMALE, RF STRAIGHT ADAPTER, PLUG-JACK |

| 6-1460821-4 | FEMALE-FEMALE, RF STRAIGHT ADAPTER, JACK-JACK |

| 6-146284-0 | 10 CONTACT(S), MALE, STRAIGHT TWO PART BOARD CONNECTOR, SOLDER |

相關代理商/技術參數 |

參數描述 |

|---|---|

| 5V80001PGGI8 | 制造商:Integrated Device Technology Inc 功能描述:PLL Frequency Synthesizer Dual 45.1584MHz to 98.304MHz 20-Pin TSSOP T/R 制造商:Integrated Device Technology Inc 功能描述:PLL FREQ SYNTHESIZER DUAL 45.1584MHZ TO 98.304MHZ 20TSSOP - Tape and Reel 制造商:Integrated Device Technology Inc 功能描述:MOST CLOCK INTERFACE |

| 5V80013NLGI | 功能描述:IC CLK GENERATION CHIP 20-TSSOP 制造商:idt, integrated device technology inc 系列:* 零件狀態(tài):有效 標準包裝:100 |

| 5V80013NLGI8 | 功能描述:IC CLK GENERATION CHIP 20-TSSOP 制造商:idt, integrated device technology inc 系列:* 零件狀態(tài):有效 標準包裝:2,500 |

| 5V80014NLGI | 功能描述:時鐘發(fā)生器及支持產品 MEMS CLOCK GENERATOR RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:QFN-56 |

| 5V80014NLGI8 | 制造商:Integrated Device Technology Inc 功能描述:MEMS CLOCK GENERATOR 制造商:Integrated Device Technology Inc 功能描述:16 QFN (GREEN) - Tape and Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。