- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄157280 > 5962G9855201QXX 32-BIT, 12 MHz, RISC MICROCONTROLLER, CPGA144 PDF資料下載

參數(shù)資料

| 型號: | 5962G9855201QXX |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 12 MHz, RISC MICROCONTROLLER, CPGA144 |

| 封裝: | CERAMIC, PGA-144 |

| 文件頁數(shù): | 38/64頁 |

| 文件大小: | 1464K |

| 代理商: | 5962G9855201QXX |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁當前第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁

43

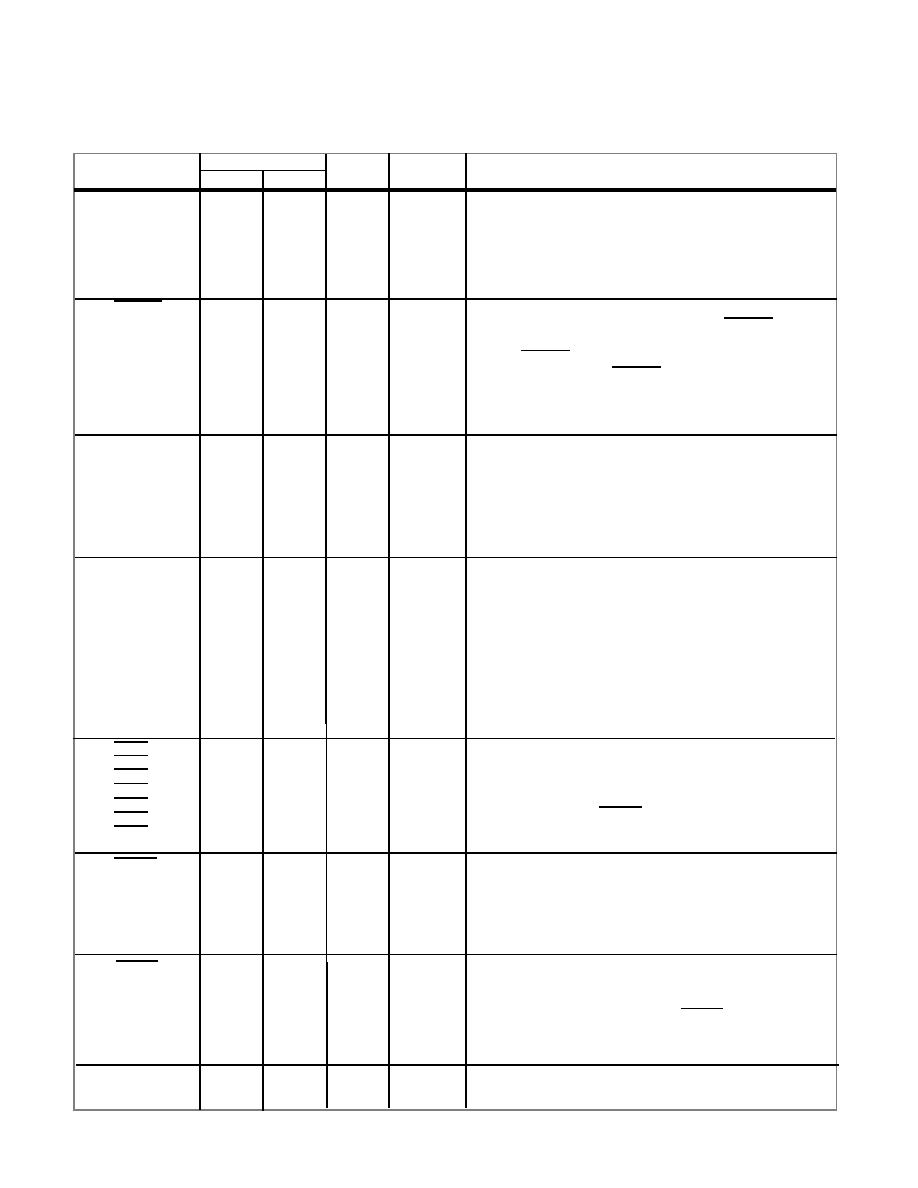

Memory Parity (Error). Asserting this input indicates a

machine error. Bit 13 of the UT69R000’s Fault

Register, is set when MCHNE2 is active. Under no

circumstances should MCHNE2 be tied in its active

state. It is tied to an internal pull-down resistor. Interrupt

is not cleared via software until the negation of the input

signal.

MCHNE1

125

G2

TUI

INTERRUPTS/EXCEPTIONS

PIN NAME

PIN NUMBER

FLTPK

PGA

TYPE

ACTIVE

DESCRIPTION

122

D1

TUI

System Fault. This positive edge-triggered input sets bit 8

(MCHNE1) in the UT69R000’s Fault Register. Under no

circumstances should MCHNE1 be tied in its active state.

It is tied to an internal pull-up resistor. Interrupt is not

cleared via software until the negation of the input signal.

MCHNE2

Bus Time Error. It is asserted when a bus error or a timeout

occurs. During I/O bus cycles, an active BTERR sets bit

10 of the Fault Register. During Memory bus cycles, an

active BTERR sets bit 7 of the Fault Register. Under no

circumstances should BTERR be tied in its active state. It

is tied to an internal pull-up resistor. Interrupt is not cleared

via software until the negation of the input signal.

124

F2

TDI

MPROT

123

F3

TUI

AH

Memory Protect Fault. When asserted, it informs the

UT69R000 that a memory-protect fault has occurred on the

Operand Data Bus. An access fault, a write-protect fault, or

an execute-protect fault causes a memory-protect fault. If the

UT69R000 is using the bus and MPROT is asserted, bit 15

of the Fault Register (CPU Fault) is set. If the UT69R000 is

not using the bus and MPROT is asserted, bit 14 of the Fault

Register (DMA Error) is set. It is tied to an internal pull-up

resistor. Interrupt is not cleared via software until the

negation of the input signal.

AL

AH

56

M15

TUI

62

J15

User Interrupts. These interrupts are active on a negative-

going pulse and each will set, when active, its associated bit

in the Pending Interrupt Register. The interrupts are

maskable by setting the associated bits in the Interrupt Mask

Register. Asserting MRST resets all interrupts. They are

tied to an internal pull-up resistor.

57

58

59

60

K13

K14

J14

J13

63

H14

55

L14

TUI

AL

Power Fail (Interrupt). Asserting this input

informs the UT69R000 that a power failure has occurred and

the present process will be interrupted. This input sets bit 15

in the Pending Interrupt Register. A Power Fail Interrupt (bit

15) cannot be disabled or masked. It is tied to an internal pull-

up resistor.

47

R14

TUI

AL

Master Reset. This input initializes the UT69R000 to a

reset state. The UT69R000 must be reset after power

(Vcc) is within specification and stable to ensure proper

operation. The system must hold MRST active for at

least one period of SYSCLK to assure the UT69R000

will be reset. It is tied to an internal pull-up resistor.

AH

AL

BTERR

INT0

INT1

INT2

INT3

INT4

INT5

INT6

INT2

PFAIL

MRST

61

K15

TUI

--

NUI4

Not used input 4. Internal UTMC use only. Tie high.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 5962G9855202VXA | 32-BIT, 16 MHz, RISC MICROCONTROLLER, CPGA144 |

| 5962G9855202VXX | 32-BIT, 16 MHz, RISC MICROCONTROLLER, CPGA144 |

| 5962H9855201VXC | 32-BIT, 12 MHz, RISC MICROCONTROLLER, CPGA144 |

| 5962H9855202QXX | 32-BIT, 16 MHz, RISC MICROCONTROLLER, CPGA144 |

| 5962H9855202VXX | 32-BIT, 16 MHz, RISC MICROCONTROLLER, CPGA144 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 5962H94A0305QXC | 制造商: 功能描述: 制造商:undefined 功能描述: |

| 5962H9853701 | 制造商: 功能描述: 制造商:undefined 功能描述: |

| 5962L0051502VHA | 制造商:Analog Devices 功能描述:AEROSPACE 7NS SINGLE COMPARATOR - Trays |

| 5962L0052401VGA | 功能描述:校驗器 IC RoHS:否 制造商:STMicroelectronics 產(chǎn)品: 比較器類型: 通道數(shù)量: 輸出類型:Push-Pull 電源電壓-最大:5.5 V 電源電壓-最小:1.1 V 補償電壓(最大值):6 mV 電源電流(最大值):1350 nA 響應(yīng)時間: 最大工作溫度:+ 125 C 安裝風格:SMD/SMT 封裝 / 箱體:SC-70-5 封裝:Reel |

| 5962L0052401VHA | 功能描述:校驗器 IC RoHS:否 制造商:STMicroelectronics 產(chǎn)品: 比較器類型: 通道數(shù)量: 輸出類型:Push-Pull 電源電壓-最大:5.5 V 電源電壓-最小:1.1 V 補償電壓(最大值):6 mV 電源電流(最大值):1350 nA 響應(yīng)時間: 最大工作溫度:+ 125 C 安裝風格:SMD/SMT 封裝 / 箱體:SC-70-5 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。