- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1887 > 100-1221-3 (Bluetechnix)CORE MOD CM-BF537E 600MHZ CONN PDF資料下載

參數(shù)資料

| 型號: | 100-1221-3 |

| 廠商: | Bluetechnix |

| 文件頁數(shù): | 34/68頁 |

| 文件大?。?/td> | 0K |

| 描述: | CORE MOD CM-BF537E 600MHZ CONN |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 模塊/板類型: | 核心模塊 |

| 其它名稱: | 100-1221 100-1221-ND |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁當(dāng)前第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁

Rev. J

|

Page 4 of 68

|

February 2014

BLACKFIN PROCESSOR CORE

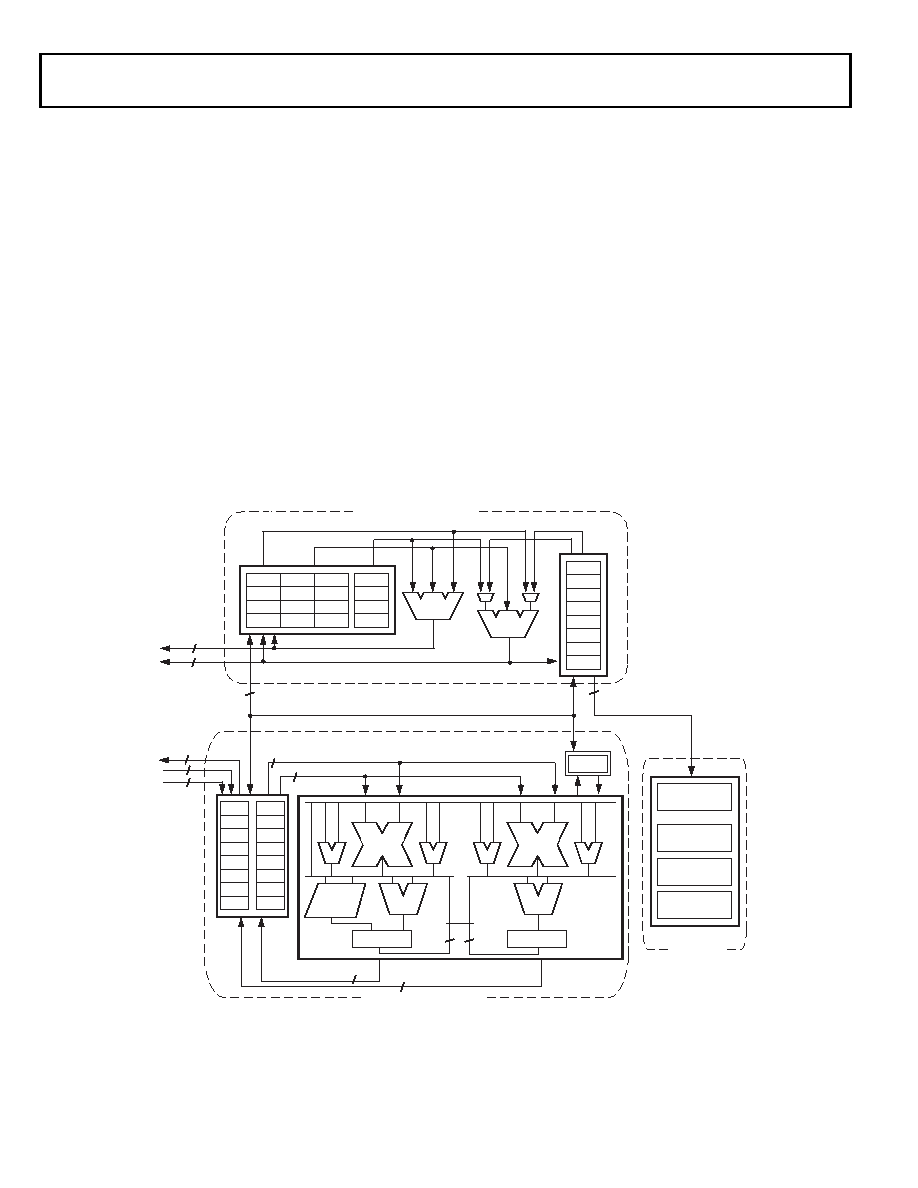

As shown in Figure 2, the Blackfin processor core contains two

16-bit multipliers, two 40-bit accumulators, two 40-bit ALUs,

four video ALUs, and a 40-bit shifter. The computation units

process 8-, 16-, or 32-bit data from the register file.

The compute register file contains eight 32-bit registers. When

performing compute operations on 16-bit operand data, the

register file operates as 16 independent 16-bit registers. All

operands for compute operations come from the multiported

register file and instruction constant fields.

Each MAC can perform a 16-bit by 16-bit multiply in each

cycle, accumulating the results into the 40-bit accumulators.

Signed and unsigned formats, rounding, and saturation

are supported.

The ALUs perform a traditional set of arithmetic and logical

operations on 16-bit or 32-bit data. In addition, many special

instructions are included to accelerate various signal processing

tasks. These include bit operations such as field extract and pop-

ulation count, modulo 232 multiply, divide primitives, saturation

and rounding, and sign/exponent detection. The set of video

instructions include byte alignment and packing operations,

16-bit and 8-bit adds with clipping, 8-bit average operations,

and 8-bit subtract/absolute value/accumulate (SAA) operations.

Also provided are the compare/select and vector search

instructions.

For certain instructions, two 16-bit ALU operations can be per-

formed simultaneously on register pairs (a 16-bit high half and

16-bit low half of a compute register). If the second ALU is used,

quad 16-bit operations are possible.

The 40-bit shifter can perform shifts and rotates, and is used to

support normalization, field extract, and field deposit

instructions.

The program sequencer controls the flow of instruction execu-

tion, including instruction alignment and decoding. For

program flow control, the sequencer supports PC relative and

indirect conditional jumps (with static branch prediction), and

subroutine calls. Hardware is provided to support zero-over-

head looping. The architecture is fully interlocked, meaning that

the programmer need not manage the pipeline when executing

instructions with data dependencies.

Figure 2. Blackfin Processor Core

SEQUENCER

ALIGN

DECODE

LOOP BUFFER

16

8

88

8

40

A0

A1

BARREL

SHIFTER

DATAARITHMETIC UNIT

CONTROL

UNIT

R7.H

R6.H

R5.H

R4.H

R3.H

R2.H

R1.H

R0.H

R7.L

R6.L

R5.L

R4.L

R3.L

R2.L

R1.L

R0.L

ASTAT

40 40

32

LD0

LD1

SD

DAG0

DAG1

ADDRESS ARITHMETIC UNIT

I3

I2

I1

I0

L3

L2

L1

L0

B3

B2

B1

B0

M3

M2

M1

M0

SP

FP

P5

P4

P3

P2

P1

P0

DA1

DA0

32

PREG

RAB

32

TO

MEMOR

Y

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 100-1225-1 | CORE MOD TCM-BF537 500MHZ CONN |

| 100-1254-2 | MODULE BF527-C-C-Q50S64F8 |

| 101-0303 | SMARTSCREEN OP7100 DISPLAY |

| 101-0383 | MODULE RABBITCORE RCM2020 |

| 101-0435 | MODULE RABBITCORE RCM2110 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 1001224 | 功能描述:防靜電控制產(chǎn)品 12X24 PKG/100 RoHS:否 制造商:3M Electronic Specialty 產(chǎn)品:Air Ionizers 類型:Mini 顏色: 大小:4.5 in x 3.3 in x 2 in |

| 1001225 | 功能描述:防靜電控制產(chǎn)品 12X25 PKG/100 RoHS:否 制造商:3M Electronic Specialty 產(chǎn)品:Air Ionizers 類型:Mini 顏色: 大小:4.5 in x 3.3 in x 2 in |

| 100-1225-1 | 功能描述:CORE MOD TCM-BF537 500MHZ CONN RoHS:是 類別:集成電路 (IC) >> 嵌入式 - 微控制器或微處理器模塊 系列:- 產(chǎn)品目錄繪圖:DLP-245SY-G 標(biāo)準(zhǔn)包裝:1 系列:USB 模塊/板類型:開發(fā)板 適用于相關(guān)產(chǎn)品:USB 其它名稱:813-1006 |

| 10-01-2259 | 功能描述:集管和線殼 KK 100 Housing Crimp Crimp Std 25 Ckt RoHS:否 產(chǎn)品種類:1.0MM Rectangular Connectors 產(chǎn)品類型:Headers - Pin Strip 系列:DF50 觸點(diǎn)類型:Pin (Male) 節(jié)距:1 mm 位置/觸點(diǎn)數(shù)量:16 排數(shù):1 安裝風(fēng)格:SMD/SMT 安裝角:Right 端接類型:Solder 外殼材料:Liquid Crystal Polymer (LCP) 觸點(diǎn)材料:Brass 觸點(diǎn)電鍍:Gold 制造商:Hirose Connector |

| 100122A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Nine Bit Buffer |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。