- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372964 > Z86C71 (ZiLOG, Inc.) IR/Low-Voltage Microcontroller PDF資料下載

參數(shù)資料

| 型號(hào): | Z86C71 |

| 廠商: | ZiLOG, Inc. |

| 英文描述: | IR/Low-Voltage Microcontroller |

| 中文描述: | 紅外/低電壓微控制器 |

| 文件頁(yè)數(shù): | 45/61頁(yè) |

| 文件大小: | 349K |

| 代理商: | Z86C71 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)當(dāng)前第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)

Z86L70/71/75/C71

Zilog

IR/Low-Voltage Microcontroller

DS97LVO0500

P R E L I M I N A R Y

1-45

1

SCLK/TCLK Divide-by-16 Select

(D0). D0 of the SMR

controls a Divide-by-16 prescaler of SCLK/TCLK. The pur-

pose of this control is to selectively reduce device power

consumption during normal processor execution (SCLK

control) and/or HALT Mode (where TCLK sources interrupt

logic). After Stop-Mode Recovery, this bit is set to a 0.

Stop-Mode Recovery Source (D2, D3, and D4).

These

three bits of the SMR specify the wake up source of the

STOP recovery (Figure 36 and Table 5).

P33-P31 cannot wake up from STOP Mode if the input

lines are configured as analog input.

Note:

Port pins defined as an output will drive the corre-

sponding input to the default state to allow the remaining

inputs to control the AND/OR function. Refer to SMR2 reg-

ister for other recover sources.

Stop-Mode Recovery Delay Select

(D5). This bit, if Low,

disables the 5 ms /RESET delay after Stop-Mode Recov-

ery. The default configuration of this bit is one. If the "fast"

wake up is selected, the Stop-Mode Recovery source

needs to be kept active for at least 5TpC.

Stop-Mode Recovery Edge Select

(D6). A 1 in this bit po-

sition indicates that a High level on any one of the recovery

sources wakes the Z86L7X from STOP Mode. A 0 indi-

cates Low level recovery. The default is 0 on POR (Figure

36).

Cold or Warm Start

(D7). This bit is set by the device

upon entering STOP Mode. It is a Read Only Flag bit. A 1

in D7 (warm) indicates that the device will awaken from a

SMR source or a WDT while in STOP Mode. A 0 in this bit

(cold) indicates that the device will be reset by a POR,

WDT while not in STOP, or the device awakened a low

voltage standby mode.

Stop-Mode Recovery Register 2

(SMR). This register

determines the mode of the Stop-Mode Recovery for

SMR2.

If SMR2 is used in conjunction with SMR, either of the

specified events will cause a Stop-Mode Recovery.

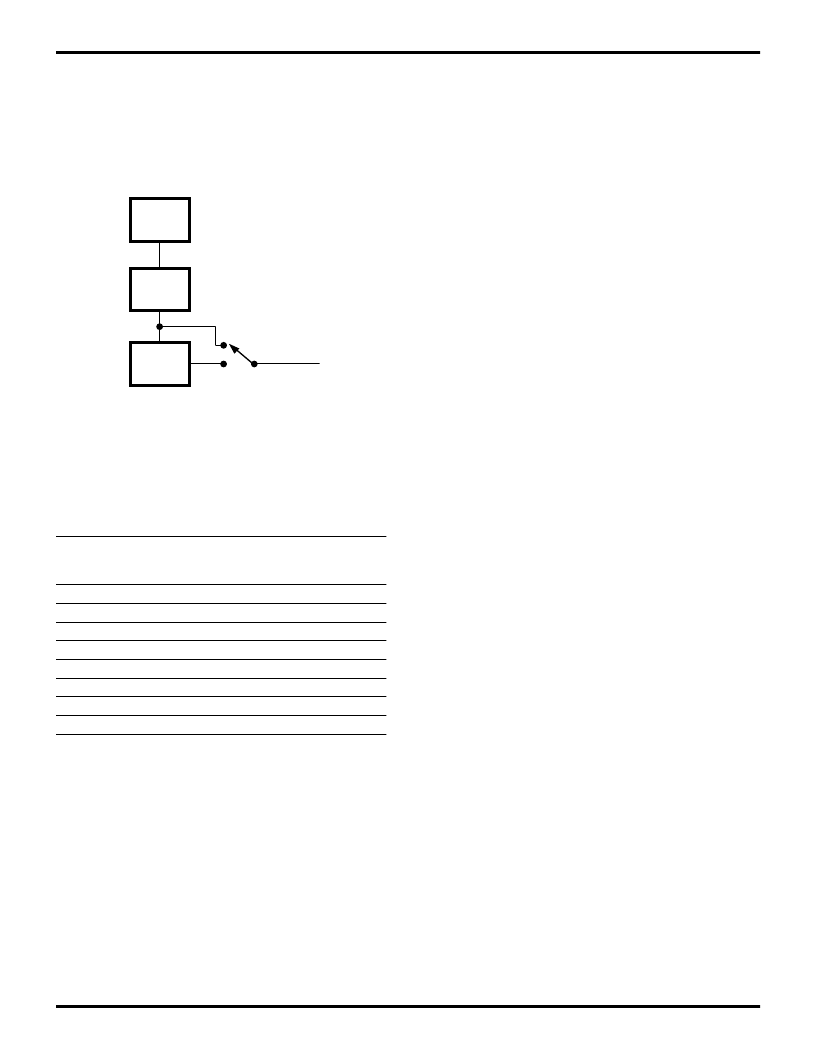

Figure 35. SCLK Circuit

Table 5. Stop-Mode Recovery Source

SMR:432

Operation

D4

0

0

0

0

1

1

1

1

D3

0

0

1

1

0

0

1

1

D2

0

1

0

1

0

1

0

1

Description of Action

POR and/or external reset recovery

Reserved

P31 transition

P32 transition

P33 transition

P27 transition

Logical NOR of P20 through P23

Logical NOR of P20 through P27

SMR, D0

÷

2

÷

16

OSC

SCLK

TCLK

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| Z86L72 | IR MICROCONTROLLER |

| Z86C7216FSC | IR MICROCONTROLLER |

| Z86L7208FSC | IR MICROCONTROLLER |

| Z86L7208PSC | IR MICROCONTROLLER |

| Z86L7208VSC | IR MICROCONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| Z86C72 | 制造商:ZILOG 制造商全稱:ZILOG 功能描述:IR MICROCONTROLLER |

| Z86C7216FSC | 制造商:ZILOG 制造商全稱:ZILOG 功能描述:IR MICROCONTROLLER |

| Z86C72-16FSC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| Z86C7216PSC | 制造商:ZILOG 制造商全稱:ZILOG 功能描述:IR MICROCONTROLLER |

| Z86C72-16PSC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。