- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄372964 > Z86C71 (ZiLOG, Inc.) IR/Low-Voltage Microcontroller PDF資料下載

參數(shù)資料

| 型號(hào): | Z86C71 |

| 廠商: | ZiLOG, Inc. |

| 英文描述: | IR/Low-Voltage Microcontroller |

| 中文描述: | 紅外/低電壓微控制器 |

| 文件頁(yè)數(shù): | 42/61頁(yè) |

| 文件大小: | 349K |

| 代理商: | Z86C71 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)當(dāng)前第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)

Z86L70/71/75/C71

IR/Low-Voltage Microcontroller

Zilog

1-42

P R E L I M I N A R Y

DS97LVO0500

FUNCTIONAL DESCRIPTION

(Continued)

HALT.

HALT turns off the internal CPU clock, but not the

XTAL oscillation. The counter/timers and external inter-

rupts IRQ0, IRQ1, IRQ2, IRQ3, and IRQ4 remain active.

The devices are recovered by interrupts, either externally

or internally generated. An interrupt request must be exe-

cuted (enabled) to exit HALT Mode. After the interrupt ser-

vice routine, the program continues from the instruction af-

ter the HALT.

STOP.

This instruction turns off the internal clock and ex-

ternal crystal oscillation and reduces the standby current

to 10

μ

A or less. STOP Mode is terminated only by a reset,

such as WDT time-out, POR, SMR, or external reset. This

causes the processor to restart the application program at

address 000CH. In order to enter STOP (or HALT) mode,

it is necessary to first flush the instruction pipeline to avoid

suspending execution in mid-instruction. To do this, the

user must execute a NOP (opcode = FFH) immediately be-

fore the appropriate sleep instruction, i.e.,

FF

6F

NOP

STOP

or

NOP

HALT

; clear the pipeline

; enter STOP Mode

FF

7F

; clear the pipeline

; enter HALT Mode

Port Configuration Register

(PCON). The PCON regis-

ter configures the comparator output on Port 3. It is locat-

ed in the expanded register file at Bank F, location 00 (Fig-

ure 32).

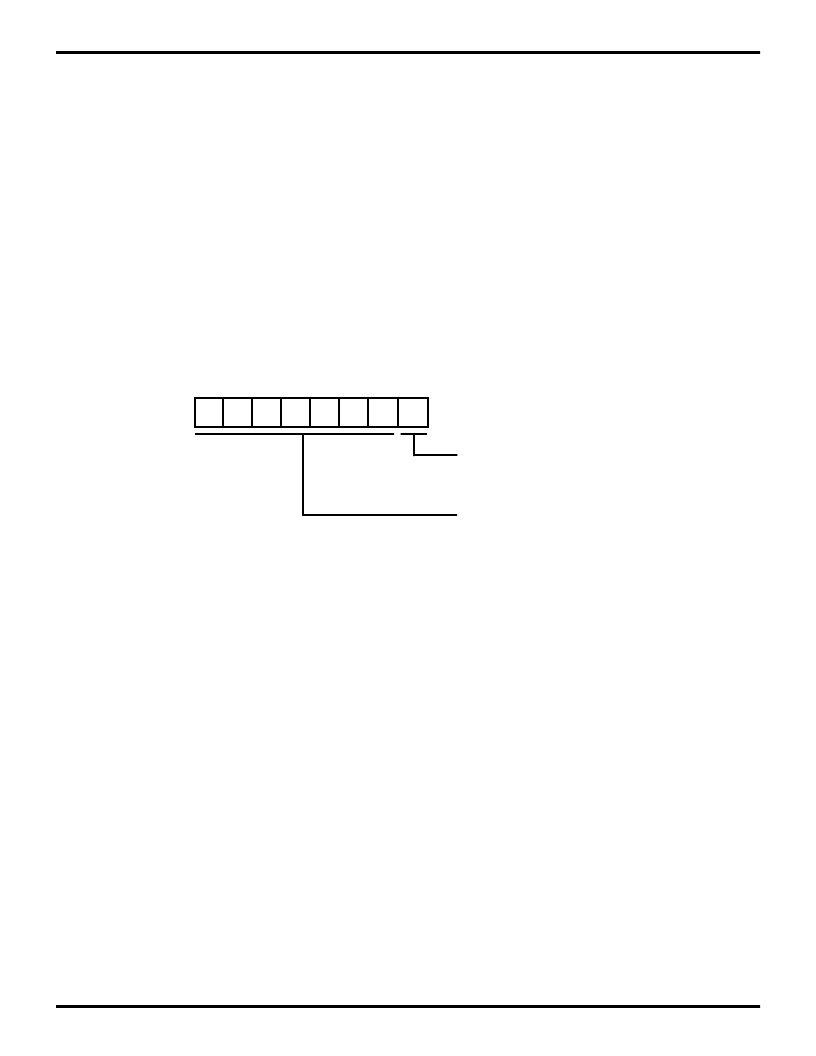

Figure 32. Port Configuration Register (PCON)

(Write Only)

Reserved (Must be 1)

D7

D6

D5

D4 D3

D2

D1

D0

PCON (FH) 00H

Comparator Output Port 3

0 P34,Standard Output*

1 P34,Comparator Output

* Default Setting After Reset

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| Z86L72 | IR MICROCONTROLLER |

| Z86C7216FSC | IR MICROCONTROLLER |

| Z86L7208FSC | IR MICROCONTROLLER |

| Z86L7208PSC | IR MICROCONTROLLER |

| Z86L7208VSC | IR MICROCONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| Z86C72 | 制造商:ZILOG 制造商全稱(chēng):ZILOG 功能描述:IR MICROCONTROLLER |

| Z86C7216FSC | 制造商:ZILOG 制造商全稱(chēng):ZILOG 功能描述:IR MICROCONTROLLER |

| Z86C72-16FSC | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:8-Bit Microcontroller |

| Z86C7216PSC | 制造商:ZILOG 制造商全稱(chēng):ZILOG 功能描述:IR MICROCONTROLLER |

| Z86C72-16PSC | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:8-Bit Microcontroller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。