- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373760 > Z5380 (ZiLOG, Inc.) Small Computer System Interface(小型計算機(jī)系統(tǒng)接口(SCSI)控制器) PDF資料下載

參數(shù)資料

| 型號: | Z5380 |

| 廠商: | ZiLOG, Inc. |

| 英文描述: | Small Computer System Interface(小型計算機(jī)系統(tǒng)接口(SCSI)控制器) |

| 中文描述: | 小型計算機(jī)系統(tǒng)接口(小型計算機(jī)系統(tǒng)接口(的SCSI)控制器) |

| 文件頁數(shù): | 8/37頁 |

| 文件大小: | 409K |

| 代理商: | Z5380 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當(dāng)前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

8

Z5380 SCSI

PS97SCC0100

Z

ILOG

FUNCTIONAL DESCRIPTION

(Continued)

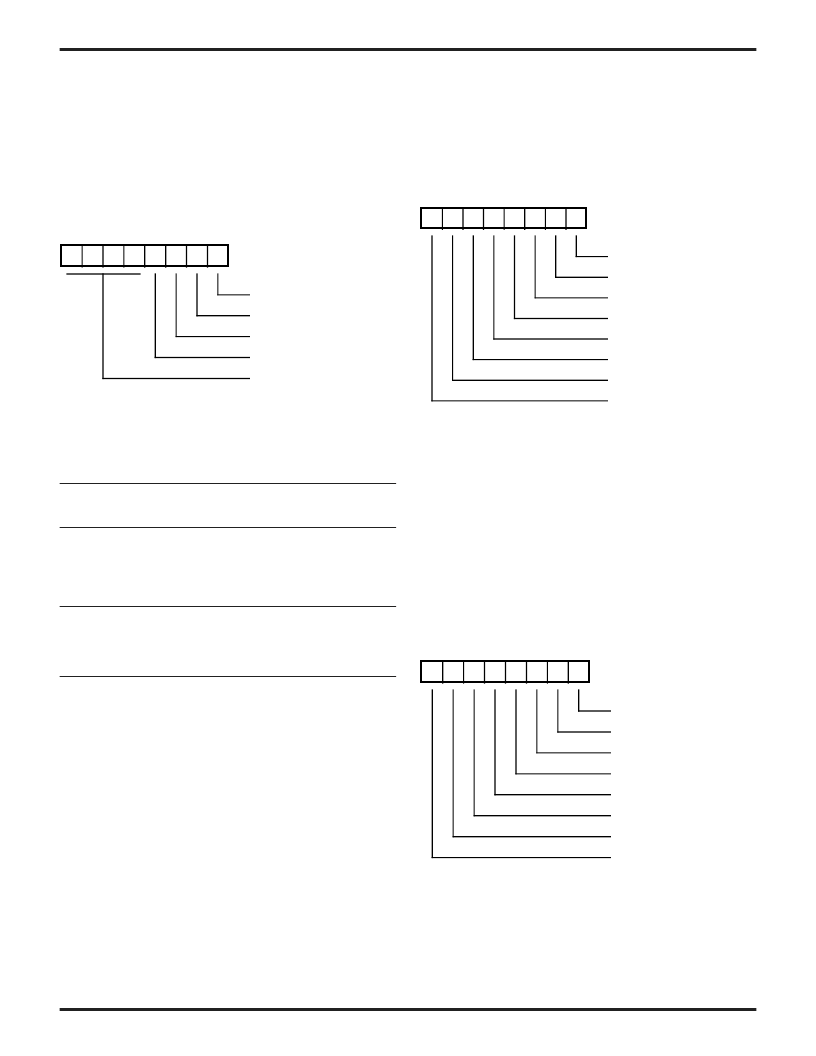

Target Command Register.

Address 3(Read/Write). When

connected as a target device, the Target Command Reg-

ister (Figure 9) allows the CPU to control the SCSI Bus

Information Transfer phase and/or to assert /REQ by writ-

ing this register. The Target Mode bit (Mode Register, bit

6) must be True (1) for bus assertion to occur. The SCSI

Bus phases are described in Table 2.

Figure 9. Target Command Register

Table 2. SCSI Information Transfer Phases

Bus Phase

Assert

I//O

Assert

C//D

Assert

/MSG

Data Out

Unspecified

Command

Message Out

0

0

0

0

0

0

1

1

0

1

0

1

Data In

Unspecified

Status

Message In

1

1

1

1

0

0

1

1

0

1

0

1

When connected as an Initiator with DMA Mode bit True, if

the phase lines (I//O, C//D, and /MSG) do not match the

phase bits in the Target Command Register, a phase

mismatch interrupt is generated when /REQ goes active.

To send data as an Initiator, the Assert I//O, Assert C//D,

and Assert /MSG bits must match the corresponding bits

in the Current SCSI Bus Status Register. The Assert /REQ

bit (bit 3) has no meaning when operating as an Initiator.

Bits 4, 5, 6, and 7 are not used.

Current SCSI Bus Status Register.

Address 4(Read

Only). The Current SCSI Bus Register is a read-only

register which is used to monitor seven SCSI Bus control

signals, plus the Data Bus parity bit. For example, an

Initiator device can use this register to determine the

current bus phase and to poll /REQ for pending data

transfers. This register may also be used to determine why

a particular interrupt occurred. Figure 10 describes the

Current SCSI Bus Status Register.

Figure 10. Current SCSI Bus Status Register

Select Enable Register.

Address 4 (Write Only). The

Select Enable Register (Figure 11) is a write-only register

which is used as a mask to monitor a signal ID during a

selection attempt. The simultaneous occurrence of the

correct ID bit, /BSY False, and /SEL True causes an

interrupt. This interrupt can be disabled by resetting all bits

in this register. If the Enable Parity Checking bit (Mode

Register, bit 5) is active (1), parity is checked during

selection.

Assert I//O

Assert C//D

Assert /MSG

Assert /REQ

"X"

Address: 3

(Read/Write)

D7 D6 D5 D4 D3 D2 D1 D0

/DBP

/SEL

I//O

C//D

/MSG

/REQ

/BSY

/RST

Address: 4

(Read Only)

D7 D6 D5 D4 D3 D2 D1 D0

/DB0

/DB1

/DB2

/DB3

/DB4

/DB5

/DB6

/DB7

Address: 4

(Write Only)

D7 D6 D5 D4 D3 D2 D1 D0

Figure 11. Select Enable Register

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| Z53C80 | SMALL COMPUTER SYSTEM INTERFACE (SCSI) |

| Z53C8003PSC | SMALL COMPUTER SYSTEM INTERFACE (SCSI) |

| Z53C8003VSC | SMALL COMPUTER SYSTEM INTERFACE (SCSI) |

| Z53C80SCSI | SMALL COMPUTER SYSTEM INTERFACE (SCSI) |

| Z54122 | RETRIGGERABLE MONOSTABLE MULTIVIBRATOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| Z538001PEC | 制造商:ZILOG 制造商全稱:ZILOG 功能描述:SMALL COMPUTER SYSTEM INTERFACE (SCSI) |

| Z538001PSC | 制造商:ZILOG 制造商全稱:ZILOG 功能描述:SMALL COMPUTER SYSTEM INTERFACE (SCSI) |

| Z538001VEC | 制造商:ZILOG 制造商全稱:ZILOG 功能描述:SMALL COMPUTER SYSTEM INTERFACE (SCSI) |

| Z538001VSC | 制造商:ZILOG 制造商全稱:ZILOG 功能描述:SMALL COMPUTER SYSTEM INTERFACE (SCSI) |

| Z5380P | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Interface IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。