- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376461 > XRT73L02MIV (EXAR CORP) TWO CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT PDF資料下載

參數(shù)資料

| 型號: | XRT73L02MIV |

| 廠商: | EXAR CORP |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | TWO CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT |

| 中文描述: | DATACOM, PCM TRANSCEIVER, PQFP100 |

| 封裝: | 14 X 14 MM, 1.40 MM HEIGHT, PLASTIC, QFP-100 |

| 文件頁數(shù): | 30/46頁 |

| 文件大小: | 391K |

| 代理商: | XRT73L02MIV |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁當(dāng)前第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁

XRT73L02M

xr

TWO CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT

REV. 1.0.0

28

5.0.2

The Clock and Data Recovery Circuit extracts the embedded clock, from the sliced digital data stream and pro-

vides the retimed data to the B3ZS (HDB3) decoder.

The Clock Recovery PLL can be in one of the following two modes:

T

RAINING

M

ODE

:

In the absence of input signals at RTIP_n and RRING_n pins, or when the frequency difference between the

recovered line clock signal and the reference clock applied on the E3/DS3/STS1CLK input pins exceed 0.5%, a

Loss of Lock condition is declared by toggling RLOL_n output pin “High” (in Hardware Mode) or setting the

RLOL_n bit to “1” in the control registers. Also, the clock output on the RxClk_n pins are the same as the refer-

ence clock applied on E3/DS3/STS1CLK pins.

D

ATA

/C

LOCK

R

ECOVERY

M

ODE

:

In the presence of input line signals on the RTIP_n and RRING_n input pins and when the frequency difference

between the recovered clock signal and the reference clock signal is less than 0.5%, the clock that is output on

the RxClk_n out pins is the Recovered Clock signal.

C

LOCK

AND

D

ATA

R

ECOVERY

:

5.0.3

The decoder block takes the output from clock and data recovery block and decodes the B3ZS (for DS3 or

STS-1) or HDB3 (for E3) encoded line signal and detects any coding errors or excessive zeros in the data

stream.

When the input signal violates the B3ZS or HDB3 coding sequence for bipolar violation or contains three (for

B3ZS) or four (for HDB3) or more consecutive zeros, an active “High” pulse is generated on the RLCV_n output

pins to indicate line code violation.

B3ZS/HDB3 D

ECODER

:

N

OTE

: In Single- Rail (NRZ) mode, the decoder is bypassed.

5.0.4

LOS (Loss of Signal) Detector:

5.0.4.1

A Digital Loss of SIgnal (DLOS) condition occurs when a string of 175 ± 75 consecutive zeros occur on the line.

When the DLOS condition occurs, the DLOS_n bit is set to “1” in the status control register. DLOS condition is

cleared when the detected average pulse density is greater than 33% for 175 ± 75 pulses.

Analog Loss of Signal (ALOS) condition occurs when the amplitude of the incoming line signal is below the

threshold as shown in the Table 10.The status of the ALOS condition is reflected in the ALOS_n status control

register.

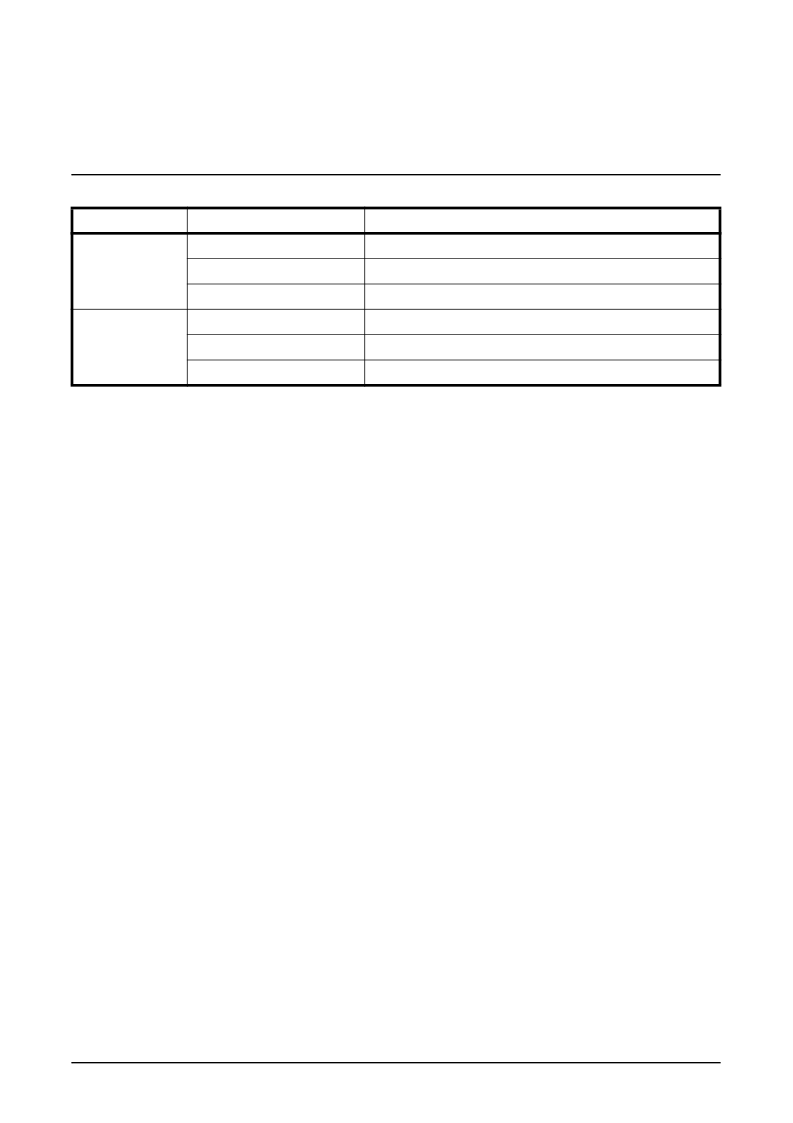

DS3/STS-1 LOS Condition:

DS3

0 feet

-16 dB

225 feet

- 15dB

450 feet

- 15dB

STS-1

0 feet

- 17 dB

225 feet

- 16 dB

450 feet

- 16 dB

T

ABLE

9: I

NTERFERENCE

M

ARGIN

T

EST

R

ESULTS

M

ODE

C

ABLE

L

ENGTH

(A

TTENUATION

)

I

NTERFERENCE

T

OLERANCE

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT73L02 | 2 Channel E3/DS3/STS-1 Line Interface Unit(2通道 E3/DS3/STS-1線接口單元) |

| XRT73L03A | 3 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT |

| XRT73L03AIV | 3 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT |

| XRT73L03B | 3 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT |

| XRT73L03BIV | 3 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT73L02MIV-F | 功能描述:外圍驅(qū)動器與原件 - PCI RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| XRT73L02MIVTR-F | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| XRT73L03 | 制造商:EXAR 制造商全稱:EXAR 功能描述:3 CHANNEL E3/DS3/STS-1 LINE INTERFCE UNIT |

| XRT73L03A | 制造商:EXAR 制造商全稱:EXAR 功能描述:3 CHANNEL DS3/E3/STS-1 LINE INTERFACE UNIT |

| XRT73L03AIV | 制造商:Exar Corporation 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。