- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376460 > XRT71D03 (EXAR CORP) 3-Channel E3/DS3/STS-1 Jitter Attenuator,STS-1 to DS3 Desynchronizer(達(dá)到E3/DS3/STS-1振蕩要求的3通道振蕩衰減器) PDF資料下載

參數(shù)資料

| 型號: | XRT71D03 |

| 廠商: | EXAR CORP |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | 3-Channel E3/DS3/STS-1 Jitter Attenuator,STS-1 to DS3 Desynchronizer(達(dá)到E3/DS3/STS-1振蕩要求的3通道振蕩衰減器) |

| 中文描述: | DATACOM, PCM JITTER ATTENUATOR, PQFP64 |

| 封裝: | 10 X 10 MM, 1.40 MM HEIGHT, LQFP-64 |

| 文件頁數(shù): | 5/20頁 |

| 文件大小: | 210K |

| 代理商: | XRT71D03 |

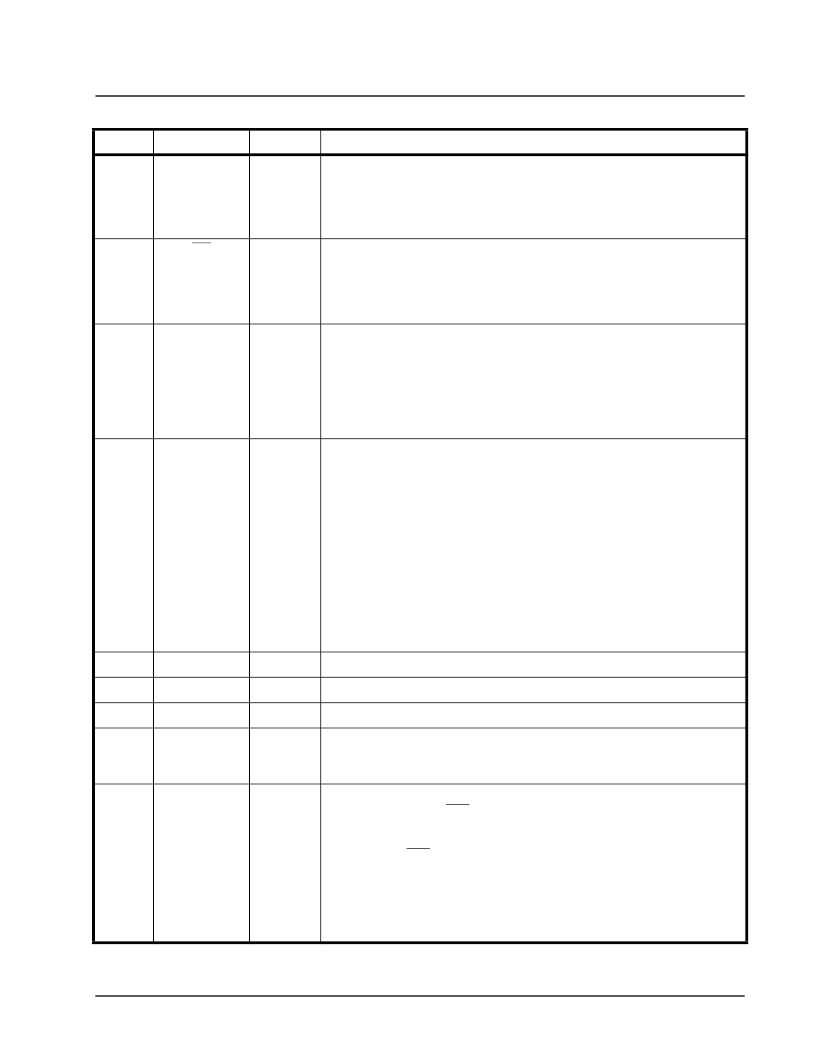

á

XRT71D03

3 CHANNEL E3/DS3/STS-1 JITTER ATTENUATOR, STS-1 TO DS3 DESYNCHRONIZER

PRELIMINARY

REV. P1.0.2

5

11

MODE_CTRL

I

Mode Control:

When “High” in Multimode, all channels are independent. When “Low”, the

Master Channel (channel0) controls DS3/E3_chn, STS1_chn, RCLKES, FSS

and MCLKn. DJA is NOT affected.

Internal 50 K Ohm pull-up resistor.

12

ICT

I

In Circuit Testing Input.

(Active low):

With this pin tied to ground, all output pins will be in high impedance mode for

in-circuit-testing.

For normal operation this input pin should be tied to VDD.

Internal 50 K Ohm pull-up resistor.

13

HOST

I

Host/Hardware Mode Select:

An active-high input enables the Host mode. Data is written to the command

registers to configure the XRT71D04.

In the Host mode, the states of discrete input pins are inactive.

An active-low input enables the Hardware Mode.In this mode, the discrete

inputs are active.

Internal 50 K Ohm pull-down resistor.

14

FLRST

I

Fifo Limit Reset

Hardware Mode

Whenever the FIFO is within 2 bits of either underflow or overflow, the FLn) will

be set high.

This pin allows the user to reset the state of FL(n), (FIFO Limit) output pin.

This pin when pulsed “High”, resets the the FL(n) output pin, (toggles to GND).

N

OTE

:

The FL(n) could be set “High” again if the FIFO is within 2 bits of either

underflow or overflow.

Host Mode

Reading the FL(n) bits in the status registers clears the FL(n) pin. Master

RESET also clears the FL(n) output.

This pin is tied to GND. FLRST has no effect in this mode.

Internal 50 K Ohm pull-down resistor.

15

VSS

****

Digital Ground

16

NC

17

AVSS

****

Analog Ground

18

FL0

O

FIFO Limit - channel 0:

This output pin is driven high whenever the internal FIFO comes within two-bits

of being underflow or overflow.

19

STS1_ch0

I

SONET STS1 Mode Select - channel 0:

This pin along with the DS3/E3_ch0 select pin configures the XRT71D04 either

in E3, DS3 or STS-1 mode.

A table relating to the setting of the pins is given below:

STS-1

DS3/E3

XRT71D04 Operating Mode

0 0 DS3 (44.736 MHz)

0 1 E3 (34.368 MHz)

1 0 STS-1 (51.84 MHz)

1 1 E3 (34.368 MHz)

This input pin is active only in the Hardware Mode

PIN DESCRIPTION

P

IN

#

N

AME

T

YPE

D

ESCRIPTION

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT71D04 | 4-Channel E3/DS3/STS-1 Jitter Attenuator,STS-1 to DS3 Desynchronizer(達(dá)到E3/DS3/STS-1振蕩要求的4通道振蕩衰減器) |

| XRT7234 | E3 ATM User Network Interface(E3異步傳輸模式用戶網(wǎng)絡(luò)接口) |

| XRT7245 | DS3 ATM User Network Interface(DS3異步傳輸模式用戶網(wǎng)絡(luò)接口) |

| XRT7288IP | CEPT1 Line Interface |

| XRT7288 | CEPT1 Line Interface(CEPT1線接口) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT71D03ES | 功能描述:時鐘合成器/抖動清除器 3CH T3/E3JA w/T73LC03A RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| XRT71D03IV | 制造商:EXAR 制造商全稱:EXAR 功能描述:3 CHANNEL E3/DS3/STS-1 JITTER ATTENUATOR |

| XRT71D03IV-F | 功能描述:時鐘合成器/抖動清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| XRT71D03IVTR-F | 功能描述:時鐘合成器/抖動清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| XRT71D04 | 制造商:EXAR 制造商全稱:EXAR 功能描述:4 CHANNEL E3/DS3/STS-1 JITTER ATTENUATOR, STS-1 TO DS3 DESYNCHRONIZER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。