- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16501 > XR16M564IV80-0A-EB (Exar Corporation)EVAL BOARD FOR XR16M564-A 80LQFP PDF資料下載

參數(shù)資料

| 型號: | XR16M564IV80-0A-EB |

| 廠商: | Exar Corporation |

| 文件頁數(shù): | 5/55頁 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD FOR XR16M564-A 80LQFP |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | * |

第1頁第2頁第3頁第4頁當(dāng)前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁

XR16M564/564D

13

REV. 1.0.0

1.62V TO 3.63V QUAD UART WITH 32-BYTE FIFO

operation by loading or unloading the FIFO in a block sequence determined by the programmed trigger level.

2.7

Crystal Oscillator or External Clock Input

The M564 includes an on-chip oscillator (XTAL1 and XTAL2) to produce a clock for both UART sections in the

device. The CPU data bus does not require this clock for bus operation. The crystal oscillator provides a

system clock to the Baud Rate Generators (BRG) section found in each of the UART. XTAL1 is the input to the

oscillator or external clock buffer input with XTAL2 pin being the output. For programming details, see

The on-chip oscillator is designed to use an industry standard microprocessor crystal (parallel resonant,

fundamental frequency with 10-22 pF capacitance load, ESR of 20-120 ohms and 100ppm frequency

tolerance) connected externally between the XTAL1 and XTAL2 pins. Typical oscillator connections are shown

in Figure 5. Alternatively, an external clock can be connected to the XTAL1 pin to clock the internal baud rate

generator for standard or custom rates. For further reading on oscillator circuit please see application note

DAN108 on EXAR’s web site.

2.8

Programmable Baud Rate Generator with Fractional Divisor

Each UART has its own Baud Rate Generator (BRG) with a prescaler for the transmitter and receiver. The

prescaler is controlled by a software bit in the MCR register. The MCR register bit-7 sets the prescaler to divide

the input crystal or external clock by 1 or 4. The output of the prescaler clocks to the BRG. The BRG further

divides this clock by a programmable divisor between 1 and (216 - 0.0625) in increments of 0.0625 (1/16) to

obtain a 16X or 8X or 4X sampling clock of the serial data rate. The sampling clock is used by the transmitter

for data bit shifting and receiver for data sampling. The BRG divisor (DLL, DLM and DLD registers) defaults to

the value of ’1’ (DLL = 0x01, DLM = 0x00 and DLD = 0x00) upon reset. Therefore, the BRG must be

TABLE 5: TXRDY# AND RXRDY# OUTPUTS IN FIFO AND DMA MODE FOR CHANNELS A-D

PINS

FCR BIT-0=0

(FIFO DISABLED)

FCR BIT-0=1 (FIFO ENABLED)

FCR BIT-3 = 0

(DMA MODE DISABLED)

FCR BIT-3 = 1

(DMA MODE ENABLED)

RXRDY#

LOW = 1 byte

HIGH = no data

LOW = at least 1 byte in FIFO

HIGH = FIFO empty

HIGH to LOW transition when FIFO reaches the

trigger level, or timeout occurs

LOW to HIGH transition when FIFO empties

TXRDY#

LOW = THR empty

HIGH = byte in THR

LOW = FIFO empty

HIGH = at least 1 byte in FIFO

LOW = FIFO has at least 1 empty location

HIGH = FIFO is full

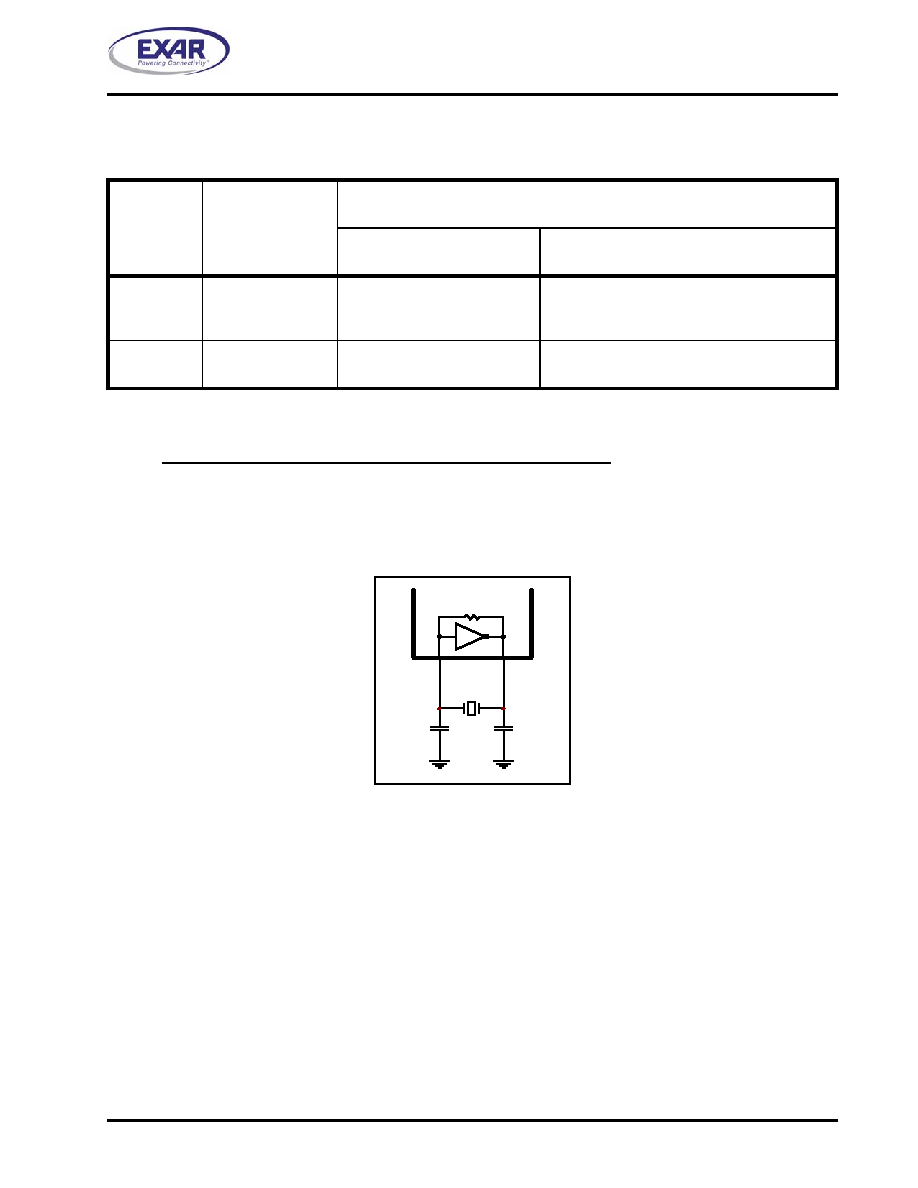

FIGURE 5. TYPICAL CRYSTAL CONNECTIONS

C1

22-47pF

C2

22-47pF

14.7456

MHz

XTAL1

XTAL2

R=300K to 400K

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| H3AKH-2036M | IDC CABLE - HSC20H/AE20M/HPK20H |

| H3BKH-5018M | IDC CABLE - HSR50H/AE50M/HPK50H |

| VI-J2M-EZ-S | CONVERTER MOD DC/DC 10V 25W |

| XR16M564IV-0B-EVB | EVAL BOARD FOR XR16M564-B 64LQFP |

| SI3056PPT-EVB | BOARD EVAL FOR DAA SI3056/SI3018 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XR16M564IV80-0B-EB | 功能描述:界面開發(fā)工具 Eval Board for XR16M564IV80-0B RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類型:RS-485 工具用于評估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

| XR16M564IV80-F | 功能描述:UART 接口集成電路 UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR16M570 | 制造商:EXAR 制造商全稱:EXAR 功能描述:1.62V TO 3.63V HIGH PERFORMANCE UART WITH 16-BYTE FIFO |

| XR16M570IB25 | 制造商:EXAR 制造商全稱:EXAR 功能描述:1.62V TO 3.63V HIGH PERFORMANCE UART WITH 16-BYTE FIFO |

| XR16M570IB25-0C-EB | 功能描述:界面開發(fā)工具 Eval Board for XR16M570IB25 Series RoHS:否 制造商:Bourns 產(chǎn)品:Evaluation Boards 類型:RS-485 工具用于評估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。