- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1974 > XCV812E-8FG900C (Xilinx Inc)IC FPGA 1.8V C-TEMP 900-FBGA PDF資料下載

參數(shù)資料

| 型號: | XCV812E-8FG900C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 73/118頁 |

| 文件大小: | 0K |

| 描述: | IC FPGA 1.8V C-TEMP 900-FBGA |

| 產(chǎn)品變化通告: | FPGA Family Discontinuation 18/Apr/2011 |

| 標準包裝: | 1 |

| 系列: | Virtex®-E EM |

| LAB/CLB數(shù): | 4704 |

| 邏輯元件/單元數(shù): | 21168 |

| RAM 位總計: | 1146880 |

| 輸入/輸出數(shù): | 556 |

| 門數(shù): | 254016 |

| 電源電壓: | 1.71 V ~ 1.89 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 900-BBGA |

| 供應(yīng)商設(shè)備封裝: | 900-FBGA |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁當前第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁

Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays

Module 3 of 4

DS025-3 (v3.0) March 21, 2014

2

R

— OBSOLETE — OBSOLETE — OBSOLETE — OBSOLETE —

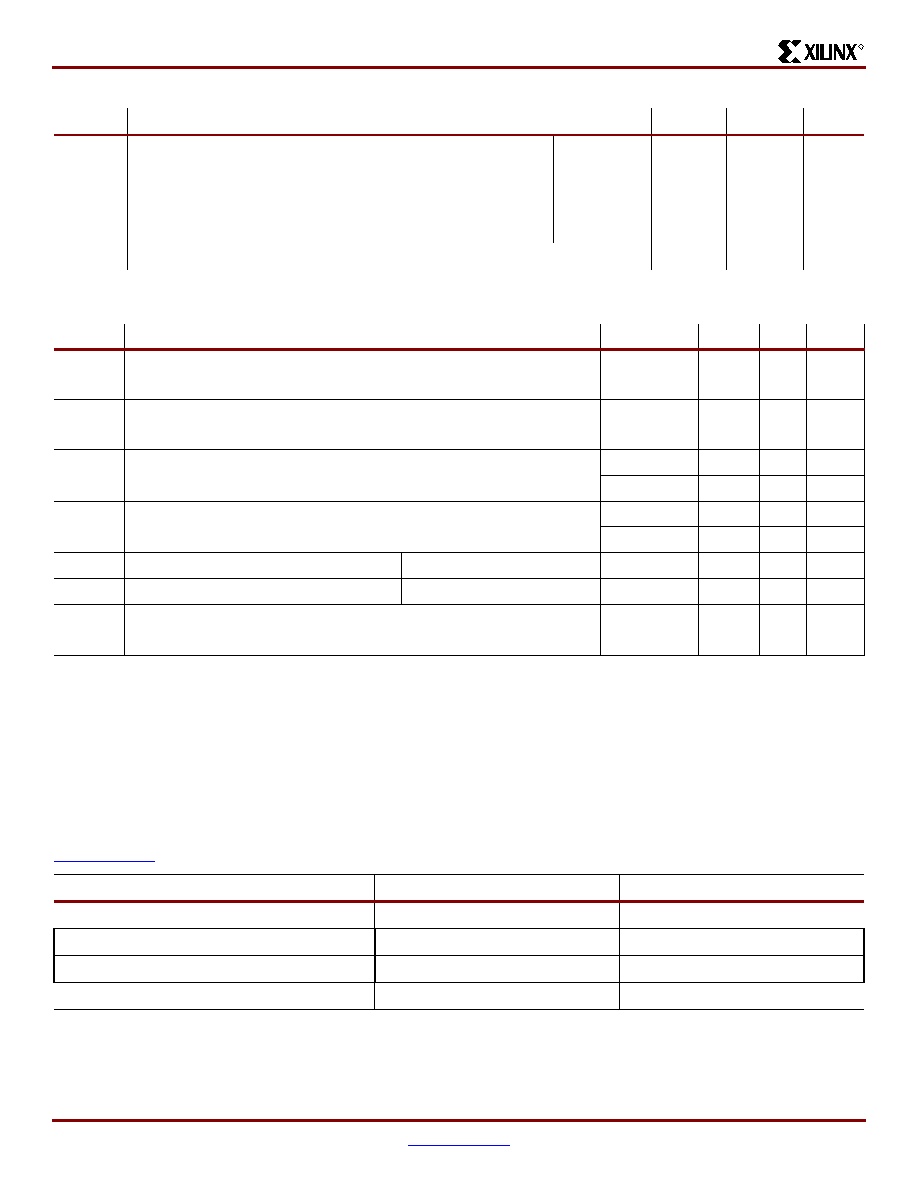

Recommended Operating Conditions

DC Characteristics Over Recommended Operating Conditions

Power-On Power Supply Requirements

Xilinx FPGAs require a certain amount of supply current during power-on to insure proper device operation. The actual

current consumed depends on the power-on ramp rate of the power supply. This is the time required to reach the nominal

power supply voltage of the device1 from 0 V. The fastest ramp rate is 0 V to nominal voltage in 2 ms and the slowest allowed

ramp rate is 0 V to nominal voltage in 50 ms. For more details on power supply requirements, see XAPP158

on

Symbol

Description

Min

Max

Units

VCCINT

Internal Supply voltage relative to GND, TJ = 0 °C to +85°C

Commercial

1.8 – 5%

1.8 + 5%

V

Internal Supply voltage relative to GND, TJ = –40°C to +100°C Industrial

1.8 – 5%

1.8 + 5%

V

VCCO

Supply voltage relative to GND, TJ = 0 °C to +85°C

Commercial

1.2

3.6

V

Supply voltage relative to GND, TJ = –40°C to +100°C

Industrial

1.2

3.6

V

TIN

Input signal transition time

250

ns

Symbol

Description(1)

Device

Min

Max

Units

VDRINT

Data Retention VCCINT Voltage

(below which configuration data might be lost)

All

1.5

V

VDRIO

Data Retention VCCO Voltage

(below which configuration data might be lost)

All

1.2

V

ICCINTQ

Quiescent VCCINT supply current1

XCV405E

400

mA

XCV812E

500

mA

ICCOQ

Quiescent VCCO supply current1

XCV405E

2

mA

XCV812E

2

mA

IL

Input or output leakage current

All

–10

+10

μA

CIN

Input capacitance (sample tested)

BGA, PQ, HQ, packages

All

8

pF

IRPU

Pad pull-up (when selected) @ Vin = 0 V, VCCO = 3.3 V (sample tested)

All

Note 2

0.25

mA

IRPD

Pad pull-down (when selected) @ Vin = 3.6 V (sample tested)

Note 2

0.25

mA

Notes:

1.

With no output current loads, no active input pull-up resistors, all I/O pins 3-stated and floating.

2.

Internal pull-up and pull-down resistors guarantee valid logic levels at unconnected input pins. These pull-up and pull-down resistors

do not guarantee valid logic levels when input pins are connected to other circuits.

Product (Commercial Grade)

Description(2)

Current Requirement(3)

XCV50E - XCV600E

Minimum required current supply

500 mA

XCV812E - XCV2000E

Minimum required current supply

1 A

XCV2600E - XCV3200E

Minimum required current supply

1.2 A

Virtex-E Family, Industrial Grade

Minimum required current supply

2 A

Notes:

1.

Ramp rate used for this specification is from 0 - 1.8 V DC. Peak current occurs on or near the internal power-on reset threshold and

lasts for less than 3 ms.

2.

Devices are guaranteed to initialize properly with the minimum current available from the power supply as noted above.

3.

Larger currents might result if ramp rates are forced to be faster.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XE8801AMI000WP | SENSING MACHINE WITH 16 + 10 BIT |

| XE8802MI035LF | IC DAS 16BIT FLASH 8K 100-LQFP |

| XE8805AMI028LF | IC DAS 16BIT FLASH 8K MTP 64LQFP |

| XE8807AMI026TLF | IC MCU LOW PWR MTP FLASH 32-TQFP |

| XIO2200AGGW | IC PCI-EXPRESS/BUS BRIDGE 176BGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XCV812E-8FG900I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCVR-040L31 | 制造商:WWP 功能描述: |

| XCW 10 | 制造商:G & J HALL 功能描述:COUNTERSINK HEXIBIT 10MM 制造商:G & J HALL 功能描述:COUNTERSINK, HEXIBIT, 10MM 制造商:G & J HALL 功能描述:COUNTERSINK, HEXIBIT, 10MM; Drill Bit Size Metric:10mm; Overall Length:30.5mm; SVHC:No SVHC (19-Dec-2012); Countersink Angle:90; Drill Bit Type:Countersink; Drill Point Diameter:10mm; External Diameter:10mm; Head Diameter:10mm; ;RoHS Compliant: NA |

| XCW10 | 制造商:G & J HALL 功能描述:COUNTERSINK HEXIBIT |

| XCW15 | 制造商:G & J HALL 功能描述:COUNTERSINK HEXIBIT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。