- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄19467 > XCR3256XL-7PQ208C (Xilinx Inc)IC CPLD 256MCELL 3.3V HP 208PQFP PDF資料下載

參數(shù)資料

| 型號(hào): | XCR3256XL-7PQ208C |

| 廠商: | Xilinx Inc |

| 文件頁(yè)數(shù): | 10/12頁(yè) |

| 文件大小: | 0K |

| 描述: | IC CPLD 256MCELL 3.3V HP 208PQFP |

| 標(biāo)準(zhǔn)包裝: | 24 |

| 系列: | CoolRunner XPLA3 |

| 可編程類型: | 系統(tǒng)內(nèi)可編程(最少 1K 次編程/擦除循環(huán)) |

| 最大延遲時(shí)間 tpd(1): | 7.0ns |

| 電壓電源 - 內(nèi)部: | 3 V ~ 3.6 V |

| 邏輯元件/邏輯塊數(shù)目: | 16 |

| 宏單元數(shù): | 256 |

| 門(mén)數(shù): | 6000 |

| 輸入/輸出數(shù): | 164 |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 208-BFQFP |

| 供應(yīng)商設(shè)備封裝: | 208-PQFP(28x28) |

| 包裝: | 托盤(pán) |

CoolRunner XPLA3 CPLD

DS012 (v2.5) May 26, 2009

Product Specification

R

JTAG Testing Capability

JTAG is the commonly used acronym for the Boundary

Scan Test (BST) feature defined for integrated circuits by

IEEE Standard 1149.1. This standard defines input/output

pins, logic control functions, and commands that facilitate

both board and device level testing without the use of spe-

cialized test equipment. CoolRunner XPLA3 devices use

the JTAG Interface for In-System Programming/Reprogram-

ming. The JTAG command set is implemented as described

in Table 4.

As implemented in CoolRunner XPLA3 CPLDs, the JTAG

Port includes four of the five pins (refer to Table 5) described

in the JTAG specification: TCK, TMS, TDI, and TDO. The

fifth signal defined by the JTAG specification is TRST (Test

Reset). TRST is considered an optional signal, since it is

not actually required to perform BST or ISP. The CoolRun-

ner XPLA3 CPLD saves an I/O pin for general purpose use

by not implementing the optional TRST signal in the JTAG

interface. Instead, the CoolRunner XPLA3 CPLD supports

the test reset functionality through the use of its power-up

reset circuit.

Port Enable Pin

The Port Enable pin is used to reclaim TMS, TDO, TDI, and

TCK for JTAG ISP programming if the user has defined

these pins as general purpose I/O during device program-

ming. For ease of use, CoolRunner XPLA3 devices are

shipped with the JTAG port pins enabled. The Port Enable

pin must be a low logic level during the power-up sequence

for the device to operate properly.

During device programming, the JTAG ISP pins can be left

as is or reconfigured as user specific I/O pins. If the JTAG

ISP pins have been used for I/O pins, simply applying a high

logic level to the Port Enable pin converts the JTAG ISP pins

back to their respective programming function and the

device can be reprogrammed via ISP. After completing the

desired JTAG ISP programming function, simply return Port

Enable to Ground to re-establish the JTAG ISP pins to their

respective I/O function. Reconfiguring the JTAG port pins as

I/Os makes these pins non-JTAG ISP functional until

reclaimed by port enable.

If the JTAG pins are not required as I/O, port enable should

be permanently tied to GND. Pins associated with the JTAG

port have internal weak pull ups enabled to terminate the

pins. However, in noisy environments, external 10K pull ups

are recommended.

The CoolRunner XPLA3 family allows the macrocells asso-

ciated with these pins to be used as buried logic when the

JTAG/ISP function is enabled.

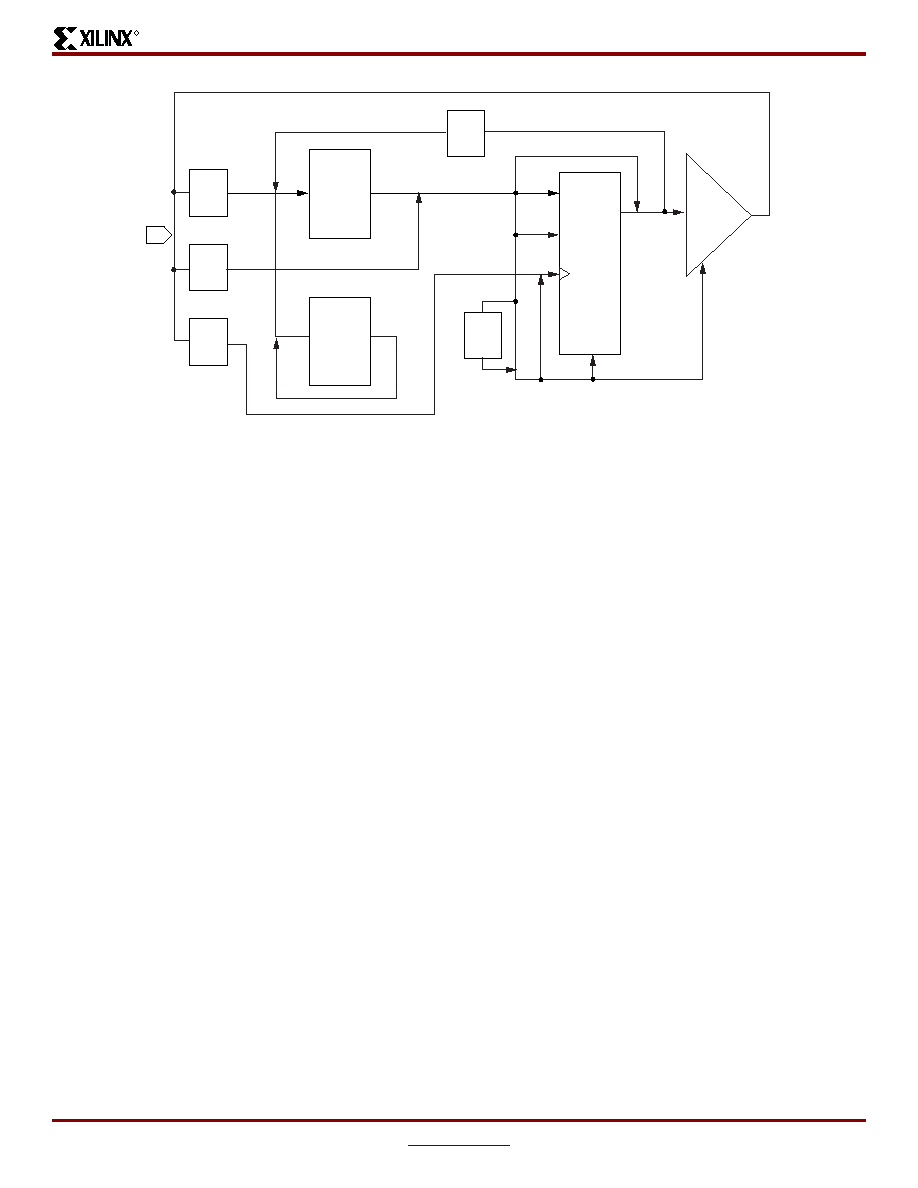

Figure 8: XPLA3 Timing Model

TIN

TF

TOUT

TEN

TSLEW

TLOGI1,2

TPTCK

DLT

Q

CE

S/R

TLOGI3

TFIN

TGCK

TUDA

DS017_02_031802

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GCC05DREN | CONN EDGECARD 10POS .100 EYELET |

| VE-21J-CY-F4 | CONVERTER MOD DC/DC 36V 50W |

| VE-B12-CX-B1 | CONVERTER MOD DC/DC 15V 75W |

| VE-B70-CY-F2 | CONVERTER MOD DC/DC 5V 50W |

| ADSP-21369BBPZ-2A | IC DSP 32BIT 333MHZ 256-BGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XCR3256XL-7PQ208I | 制造商:XILINX 制造商全稱:XILINX 功能描述:256 Macrocell CPLD |

| XCR3256XL-7PQ256C | 制造商:XILINX 制造商全稱:XILINX 功能描述:256 Macrocell CPLD |

| XCR3256XL-7PQ256I | 制造商:XILINX 制造商全稱:XILINX 功能描述:256 Macrocell CPLD |

| XCR3256XL-7PQ280C | 制造商:XILINX 制造商全稱:XILINX 功能描述:256 Macrocell CPLD |

| XCR3256XL-7PQ280I | 制造商:XILINX 制造商全稱:XILINX 功能描述:256 Macrocell CPLD |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。