- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4158 > XC4013XL-1PQ208C (Xilinx Inc)IC FPGA C-TEMP 3.3V 1SPD 208PQFP PDF資料下載

參數(shù)資料

| 型號: | XC4013XL-1PQ208C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 4/16頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA C-TEMP 3.3V 1SPD 208PQFP |

| 產(chǎn)品變化通告: | Product Discontinuation 27/Apr/2010 |

| 標準包裝: | 1 |

| 系列: | XC4000E/X |

| LAB/CLB數(shù): | 576 |

| 邏輯元件/單元數(shù): | 1368 |

| RAM 位總計: | 18432 |

| 輸入/輸出數(shù): | 160 |

| 門數(shù): | 13000 |

| 電源電壓: | 3 V ~ 3.6 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 208-BFQFP |

| 供應商設備封裝: | 208-PQFP(28x28) |

R

XC4000E and XC4000X Series Field Programmable Gate Arrays

6-84

DS005 (v2.0) March 1, 2013 - Product Specification

Product Obsolete/Under Obsolescence

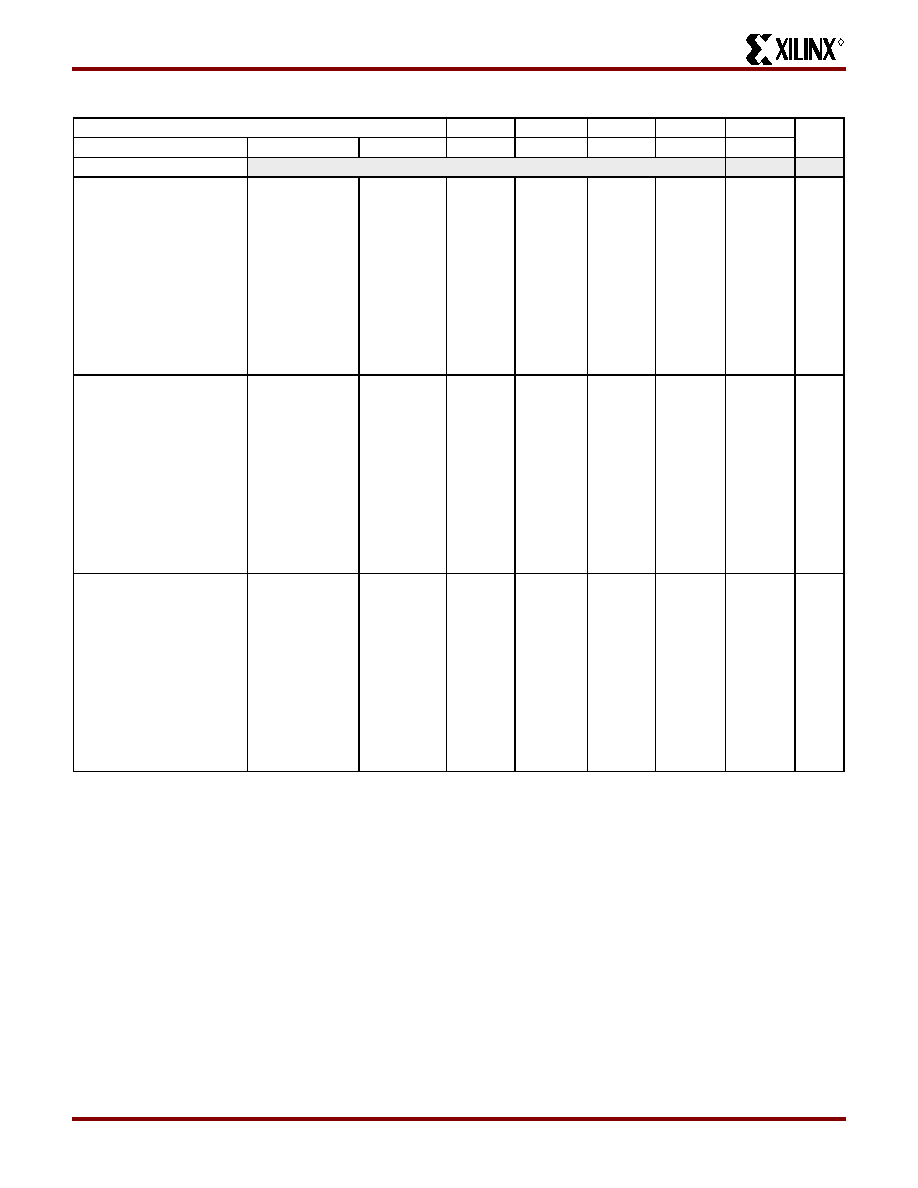

Global Early Clock BUFGEs 3, 4, 7, and 8 Set-up and Hold for IFF and FCL

Speed Grade

-3

-2

-1

-09

-08

Units

Description

Symbol

Device

Min

Input Setup & Hold Times

No Delay

Global Early Clock and

IFF

Global Early Clock and

FCL

TPSEN/TPHEN

TPFSEN/TPFHEN

XC4002XL

XC4005XL

XC4010XL

XC4013XL

XC4020XL

XC4028XL

XC4036XL

XC4044XL

XC4052XL

XC4062XL

XC4085XL

3.0 / 2.0

1.2 / 4.1

1.2 / 4.4

1.2 / 4.7

1.2 / 4.6

1.2 / 5.3

1.2 / 6.7

1.2 / 6.5

1.2 / 6.7

1.2 / 8.4

1.2 / 8.7

2.6 / 1.7

1.1 / 3.6

1.1 / 3.8

1.1 / 4.1

1.1 / 4.0

1.1 / 4.6

1.1 / 5.8

1.1 / 5.7

1.1 / 5.8

1.1 / 7.3

1.1 / 7.5

2.3 / 1.5

0.9 / 3.1

0.9 / 3.3

0.9 / 3.6

0.9 / 3.5

0.9 / 4.0

0.9 / 5.1

0.9 / 4.9

0.9 / 5.1

0.9 / 6.3

0.9 / 6.6

2.0 / 1.3

0.8 / 2.7

0.8 / 2.9

0.8 / 3.1

0.8 / 3.0

0.8 / 3.5

0.8 / 4.4

0.8 / 4.3

0.8 / 4.4

0.8 / 5.5

0.8 / 5.7

0.5 / 2.7

0.5 / 3.7

0.5 / 4.7

ns

Partial Delay

Global Early Clock and

IFF

Global Early Clock and

FCL

TPSEP/TPHEP

TPFSEP/TPFHEP

XC4002XL

XC4005XL

XC4010XL

XC4013XL*

XC4020XL

XC4028XL

XC4036XL*

XC4044XL

XC4052XL

XC4062XL*

XC4085XL

7.3 / 1.5

8.4 / 0.0

10.3 / 0.0

5.4 / 0.0

9.8 / 0.0

12.7 / 0.0

6.4 / 0.8

13.8 / 0.0

14.5 / 0.0

8.4 / 1.5

14.5 / 0.0

6.4 / 1.3

7.9 / 0.0

9.0 / 0.0

4.9 / 0.0

9.3 / 0.0

11.0 / 0.0

5.9 / 0.8

12.0 / 0.0

12.7 / 0.0

7.9 / 1.5

12.7 / 0.0

5.5 / 1.2

7.4 / 0.0

7.8 / 0.0

4.4 / 0.0

8.8 / 0.0

9.6 / 0.0

5.4 / 0.8

10.4 / 0.0

11.0 / 0.0

7.4 / 1.5

11.0 / 0.0

4.8 / 1.0

7.2 / 0.0

7.4 / 0.0

4.3 / 0.0

8.5 / 0.0

9.3 / 0.0

5.0 / 0.8

10.2 / 0.0

10.7 / 0.0

6.8 / 1.5

10.8 / 0.0

4.0 / 0.0

4.6 / 0.2

6.2 / 0.0

ns

Full Delay

Global Early Clock and

IFF

TPSED/TPHED

XC4002XL

XC4005XL

XC4010XL

XC4013XL*

XC4020XL

XC4028XL

XC4036XL*

XC4044XL

XC4052XL

XC4062XL*

XC4085XL

5.9 / 0.0

10.8 / 0.0

10.3 / 0.0

10.0 / 0.0

12.0 / 0.0

12.6 / 0.0

12.2 / 0.0

13.8 / 0.0

14.1 / 0.0

13.1 / 0.0

17.9 / 0.0

5.2 / 0.0

9.4 / 0.0

9.0 / 0.0

8.7 / 0.0

10.4 / 0.0

11.0 / 0.0

10.6 / 0.0

12.0 / 0.0

12.3 / 0.0

11.4 / 0.0

15.6 / 0.0

4.5 / 0.0

8.2 / 0.0

7.8 / 0.0

7.6 / 0.0

9.1 / 0.0

9.5 / 0.0

9.2 / 0.0

10.5 / 0.0

10.7 / 0.0

9.9 / 0.0

13.6 / 0.0

3.9 / 0.0

7.1 / 0.0

6.8 / 0.0

6.6 / 0.0

7.9 / 0.0

8.3 / 0.0

8.0 / 0.0

9.1 / 0.0

9.3 / 0.0

8.6 / 0.0

11.8 / 0.0

6.0 / 0.0

7.2 / 0.0

7.8 / 0.0

ns

* The XC4013XL, XC4036XL, and 4062XL have significantly faster partial and full delay setup times than other devices.

IFF = Input Flip Flop or Latch. FCL = Fast Capture Latch

Notes:

Input setup time is measured with the fastest route and the lightest load.

Input hold time is measured using the furthest distance and a reference load of one clock pin per IOB as well as driving all

accessible CLB flip-flops. For designs with a smaller number of clock loads, the pad-to-IOB clock pin delay as determined

by the static timing analyzer (TRCE) can be used as a worst-case pin-to-pin no-delay input hold specification.

相關PDF資料 |

PDF描述 |

|---|---|

| XC4013XL-1PQ160I | IC FPGA I-TEMP 3.3V 1SPD 160PQFP |

| ABB108DHFR | CONN EDGECARD 216POS .050 SMD |

| XC4013XL-1PQ160C | IC FPGA C-TEMP 3.3V 1SPD 160PQFP |

| XC4013XL-1HT176I | IC FPGA I 3.3V 1SPD 176HTQFP |

| XC4013XL-1HT176C | IC FPGA C 3.3V 1SPD 176HTQFP |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| XC4013XL-1PQ208C-0630 | 制造商:Xilinx 功能描述: |

| XC4013XL-1PQ208C0907 | 制造商:Xilinx 功能描述: |

| XC4013XL-1PQ208I | 功能描述:IC FPGA I-TEMP 3.3V 1SPD 208PQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:XC4000E/X 標準包裝:1 系列:Kintex-7 LAB/CLB數(shù):25475 邏輯元件/單元數(shù):326080 RAM 位總計:16404480 輸入/輸出數(shù):350 門數(shù):- 電源電壓:0.97 V ~ 1.03 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:900-BBGA,F(xiàn)CBGA 供應商設備封裝:900-FCBGA(31x31) 其它名稱:122-1789 |

| XC4013XL-1PQ208M | 制造商:XILINX 制造商全稱:XILINX 功能描述:XC4000E and XC4000X Series Field Programmable Gate Arrays |

| XC4013XL1PQ240C | 制造商:XILINX 功能描述:* |

發(fā)布緊急采購,3分鐘左右您將得到回復。