- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4280 > XC3S500E-4FTG256I (Xilinx Inc)IC FPGA SPARTAN-3E 500K 256FTBGA PDF資料下載

參數(shù)資料

| 型號(hào): | XC3S500E-4FTG256I |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 112/227頁 |

| 文件大小: | 0K |

| 描述: | IC FPGA SPARTAN-3E 500K 256FTBGA |

| 標(biāo)準(zhǔn)包裝: | 90 |

| 系列: | Spartan®-3E |

| LAB/CLB數(shù): | 1164 |

| 邏輯元件/單元數(shù): | 10476 |

| RAM 位總計(jì): | 368640 |

| 輸入/輸出數(shù): | 190 |

| 門數(shù): | 500000 |

| 電源電壓: | 1.14 V ~ 1.26 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 100°C |

| 封裝/外殼: | 256-LBGA |

| 供應(yīng)商設(shè)備封裝: | 256-FTBGA |

| 配用: | 122-1536-ND - KIT STARTER SPARTAN-3E |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁當(dāng)前第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁第215頁第216頁第217頁第218頁第219頁第220頁第221頁第222頁第223頁第224頁第225頁第226頁第227頁

DS312 (v4.1) July 19, 2013

Product Specification

2

Copyright 2005–2013 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, Artix, Kintex, Zynq, Vivado, and other designated brands included herein are trademarks of Xilinx

in the United States and other countries. PCI and PCI-X are trademarks of PCI-SIG and used under license. All other trademarks are the property of their respective owners.

Introduction

The Spartan-3E family of Field-Programmable Gate

Arrays (FPGAs) is specifically designed to meet the needs

of high volume, cost-sensitive consumer electronic

applications. The five-member family offers densities

ranging from 100,000 to 1.6 million system gates, as shown

in Table 1.

The Spartan-3E family builds on the success of the earlier

Spartan-3 family by increasing the amount of logic per I/O,

significantly reducing the cost per logic cell. New features

improve system performance and reduce the cost of

configuration. These Spartan-3E FPGA enhancements,

combined with advanced 90 nm process technology, deliver

more functionality and bandwidth per dollar than was

previously possible, setting new standards in the

programmable logic industry.

Because of their exceptionally low cost, Spartan-3E FPGAs

are ideally suited to a wide range of consumer electronics

applications, including broadband access, home

networking, display/projection, and digital television

equipment.

The Spartan-3E family is a superior alternative to mask

programmed ASICs. FPGAs avoid the high initial cost, the

lengthy development cycles, and the inherent inflexibility of

conventional ASICs. Also, FPGA programmability permits

design upgrades in the field with no hardware replacement

necessary, an impossibility with ASICs.

Features

Very low cost, high-performance logic solution for

high-volume, consumer-oriented applications

Proven advanced 90-nanometer process technology

Multi-voltage, multi-standard SelectIO interface pins

Up to 376 I/O pins or 156 differential signal pairs

LVCMOS, LVTTL, HSTL, and SSTL single-ended signal

standards

3.3V, 2.5V, 1.8V, 1.5V, and 1.2V signaling

622+ Mb/s data transfer rate per I/O

True LVDS, RSDS, mini-LVDS, differential HSTL/SSTL

differential I/O

Enhanced Double Data Rate (DDR) support

DDR SDRAM support up to 333 Mb/s

Abundant, flexible logic resources

Densities up to 33,192 logic cells, including optional shift

register or distributed RAM support

Efficient wide multiplexers, wide logic

Fast look-ahead carry logic

Enhanced 18 x 18 multipliers with optional pipeline

IEEE 1149.1/1532 JTAG programming/debug port

Hierarchical SelectRAM memory architecture

Up to 648 Kbits of fast block RAM

Up to 231 Kbits of efficient distributed RAM

Up to eight Digital Clock Managers (DCMs)

Clock skew elimination (delay locked loop)

Frequency synthesis, multiplication, division

High-resolution phase shifting

Wide frequency range (5 MHz to over 300 MHz)

Eight global clocks plus eight additional clocks per each half

of device, plus abundant low-skew routing

Configuration interface to industry-standard PROMs

Low-cost, space-saving SPI serial Flash PROM

x8 or x8/x16 parallel NOR Flash PROM

Low-cost Xilinx Platform Flash with JTAG

MicroBlaze and PicoBlaze

embedded processor cores

Fully compliant 32-/64-bit 33 MHz PCI support (66 MHz in

some devices)

Low-cost QFP and BGA packaging options

Common footprints support easy density migration

Pb-free packaging options

XA Automotive version available

8

Spartan-3E FPGA Family:

Introduction and Ordering Information

DS312 (v4.1) July 19, 2013

Product Specification

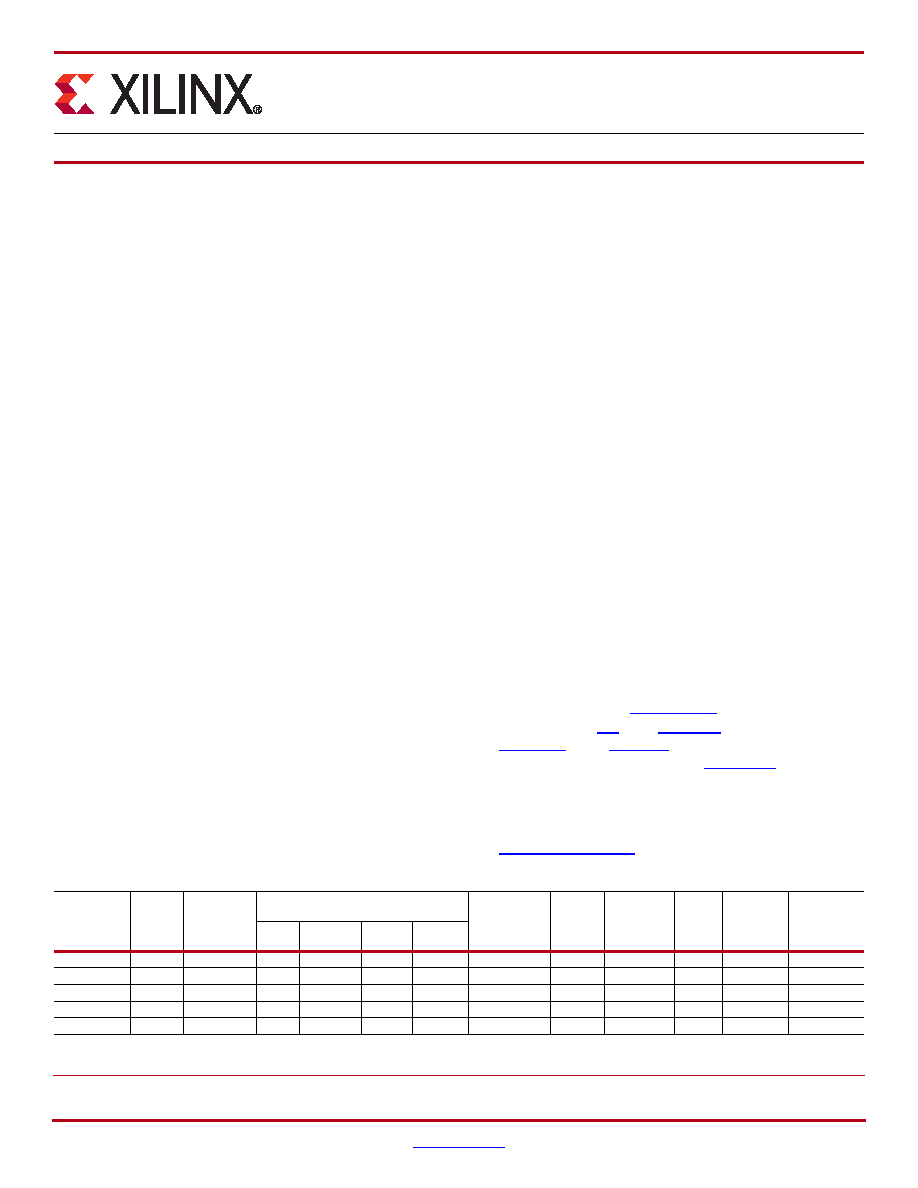

Table 1: Summary of Spartan-3E FPGA Attributes

Device

System

Gates

Equivalent

Logic Cells

CLB Array

(One CLB = Four Slices)

Distributed

RAM bits(1)

Block

RAM

bits(1)

Dedicated

Multipliers

DCMs

Maximum

User I/O

Maximum

Differential

I/O Pairs

Rows Columns

Total

CLBs

Total

Slices

XC3S100E

100K

2,160

22

16

240

960

15K

72K

4

2

108

40

XC3S250E

250K

5,508

34

26

612

2,448

38K

216K

12

4

172

68

XC3S500E

500K

10,476

46

34

1,164

4,656

73K

360K

20

4

232

92

XC3S1200E

1200K

19,512

60

46

2,168

8,672

136K

504K

28

8

304

124

XC3S1600E

1600K

33,192

76

58

3,688

14,752

231K

648K

36

8

376

156

Notes:

1.

By convention, one Kb is equivalent to 1,024 bits.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC2S200E-6PQ208I | IC FPGA 1.8V 1176 CLB'S 208-PQFP |

| 5205817-1 | CONN SCREWLOCK FEMALE 2 SETS/BAG |

| XC6SLX25-N3FTG256C | IC FPGA SPARTAN-6 256FBGA |

| XC2V40-5CSG144C | IC FPGA VIRTEX-II 40K 144-CSBGA |

| 5745563-1 | CONN D-SUB FEMALE SCREW LOCK |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC3S500E-4PQ208C | 制造商:Xilinx 功能描述:FPGA SPARTAN-3E 500K GATES 10476 CELLS 572MHZ 90NM 1.2V 208P - Trays |

| XC3S500E-4PQ208CES | 制造商:Xilinx 功能描述: |

| XC3S500E-4PQ208I | 功能描述:IC FPGA SPARTAN 3E 208PQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3E 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計(jì):2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XC3S500E-4PQG208C | 功能描述:IC SPARTAN-3E FPGA 500K 208-PQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3E 標(biāo)準(zhǔn)包裝:60 系列:XP LAB/CLB數(shù):- 邏輯元件/單元數(shù):10000 RAM 位總計(jì):221184 輸入/輸出數(shù):244 門數(shù):- 電源電壓:1.71 V ~ 3.465 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:388-BBGA 供應(yīng)商設(shè)備封裝:388-FPBGA(23x23) 其它名稱:220-1241 |

| XC3S500E-4PQG208I | 功能描述:IC FPGA SPARTAN-3E 500K 208-PQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3E 標(biāo)準(zhǔn)包裝:24 系列:ECP2 LAB/CLB數(shù):1500 邏輯元件/單元數(shù):12000 RAM 位總計(jì):226304 輸入/輸出數(shù):131 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:208-BFQFP 供應(yīng)商設(shè)備封裝:208-PQFP(28x28) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。